# Operating Systems Memory Virtualisation Base & Bounds + Segmentation

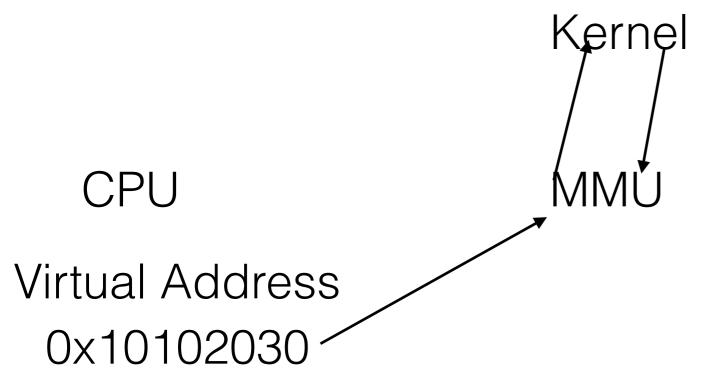

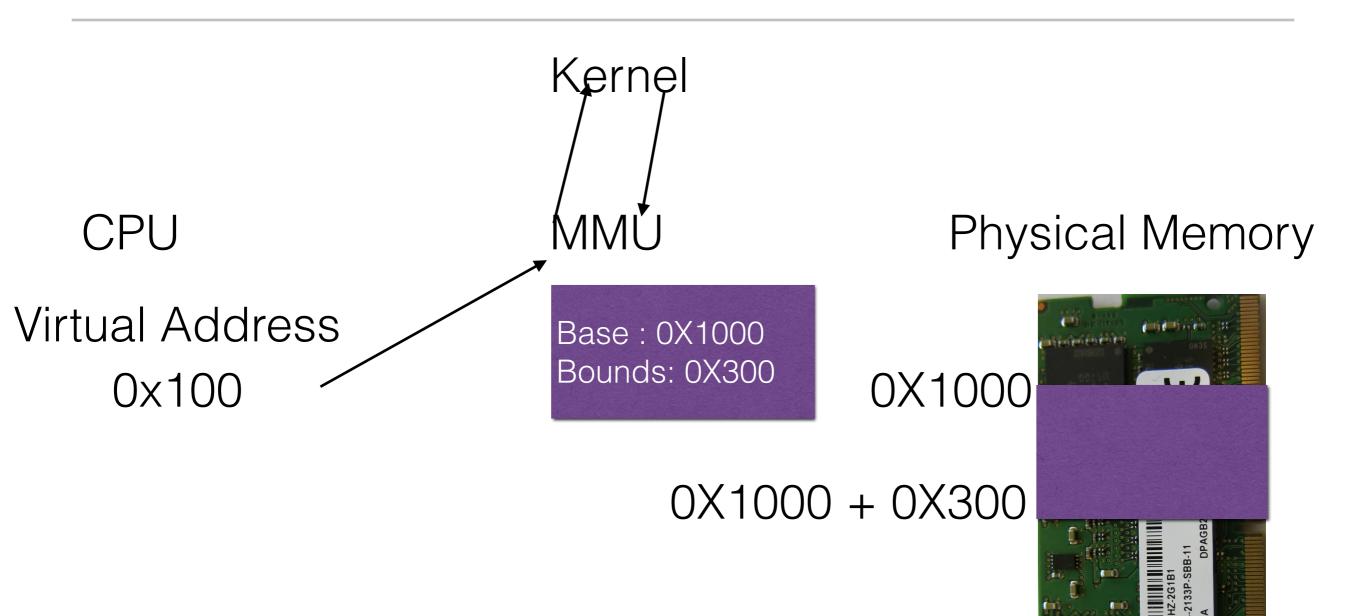

Kernel

CPU

MMU

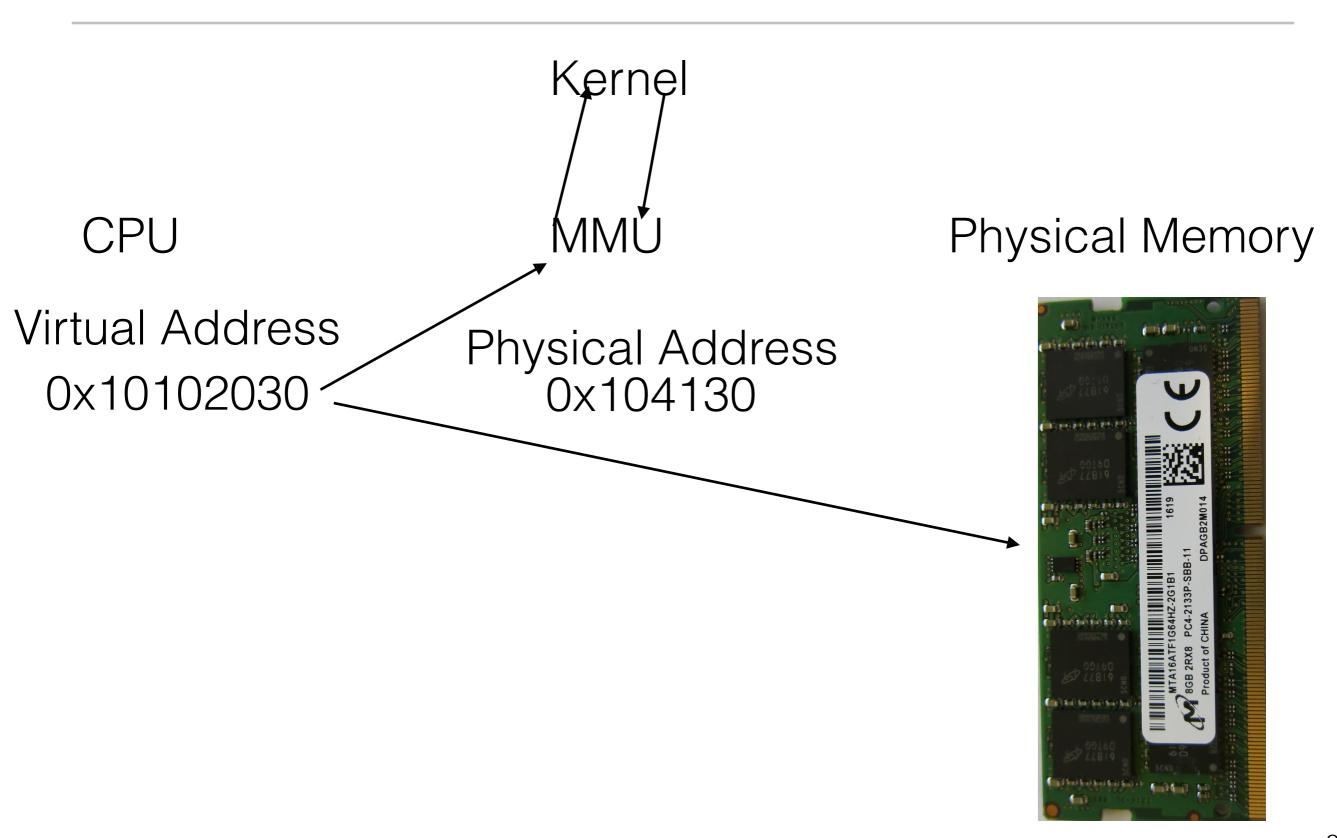

Kernel

CPU

MMU

Physical Memory

Virtual Address

Kernel

MMU

CPU

Physical Memory

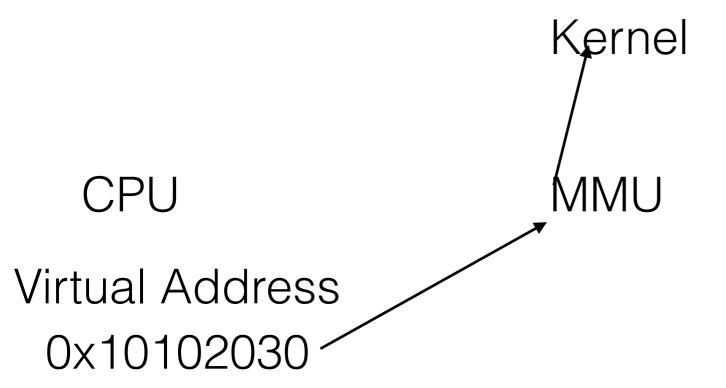

Virtual Address 0x10102030

Kernel

CPU MMU

Virtual Address

0x10102030

CPU MMU

Virtual Address

0x10102030 Physical Address

CPU MMU

Virtual Address

0x10102030 Physical Address

0x104130

Kernel **CPU** Virtual Address Physical Address 0x104130 0x10102030 What if you want to translate same virtual address again?

Kernel **CPU** Physical Memory Virtual Address Physical Address 0x104130 0x10102030 What if you want to translate same virtual address again?

Kernel **CPU** Virtual Address Physical Address 0x104130 0x10102030 What if you want to translate same virtual address again?

Physical Memory

Cache!!

Kernel **CPU** Virtual Address Physical Address 0x104130 0x10102030 What do you do with cache if there

Physical Memory

What do you do with cache if there is a context switch?

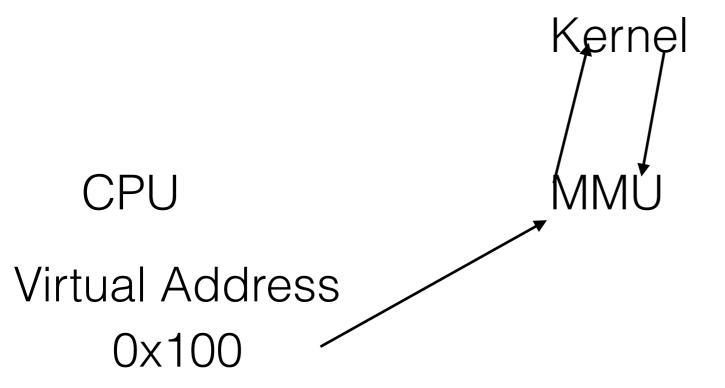

Kernel

CPU MMU

Kernel

CPU

MMU

Physical Memory

Virtual Address

Kernel

CPU

MMU

Physical Memory

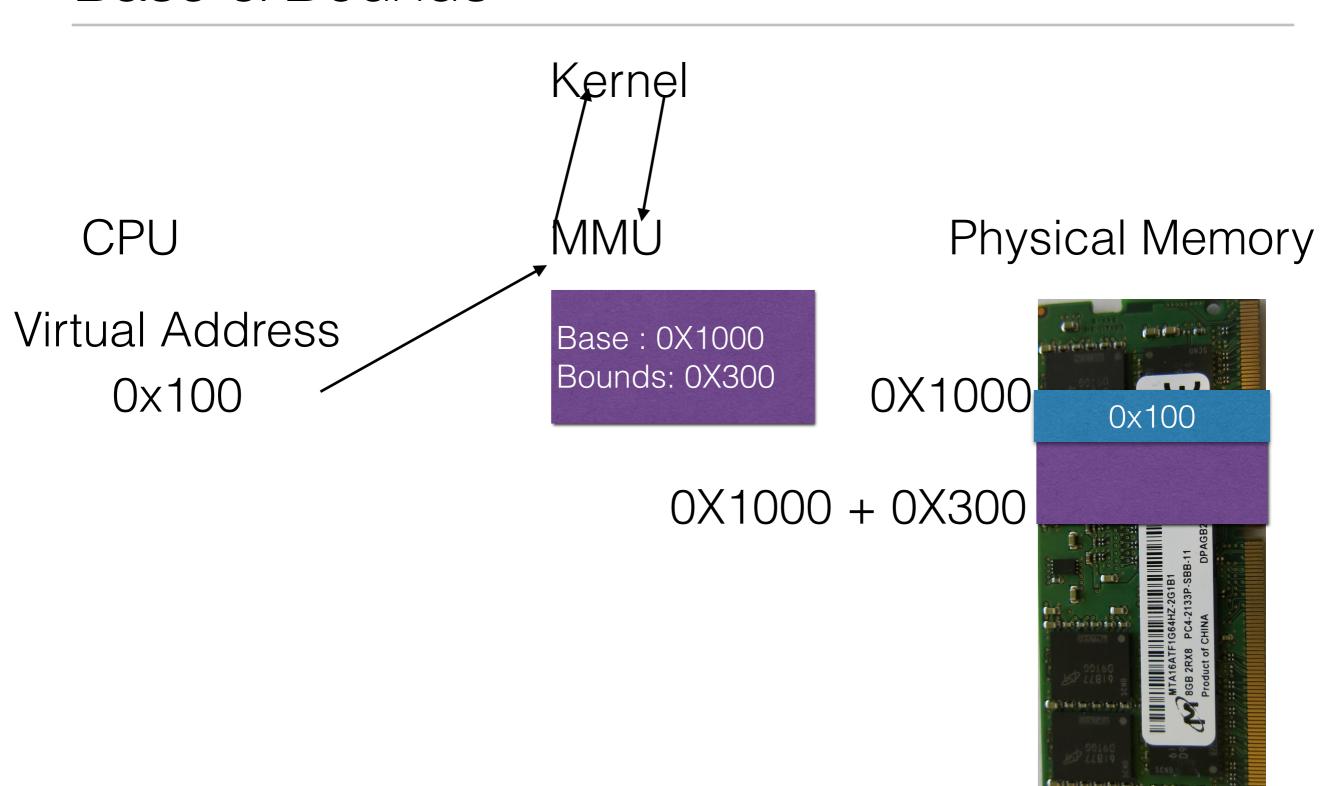

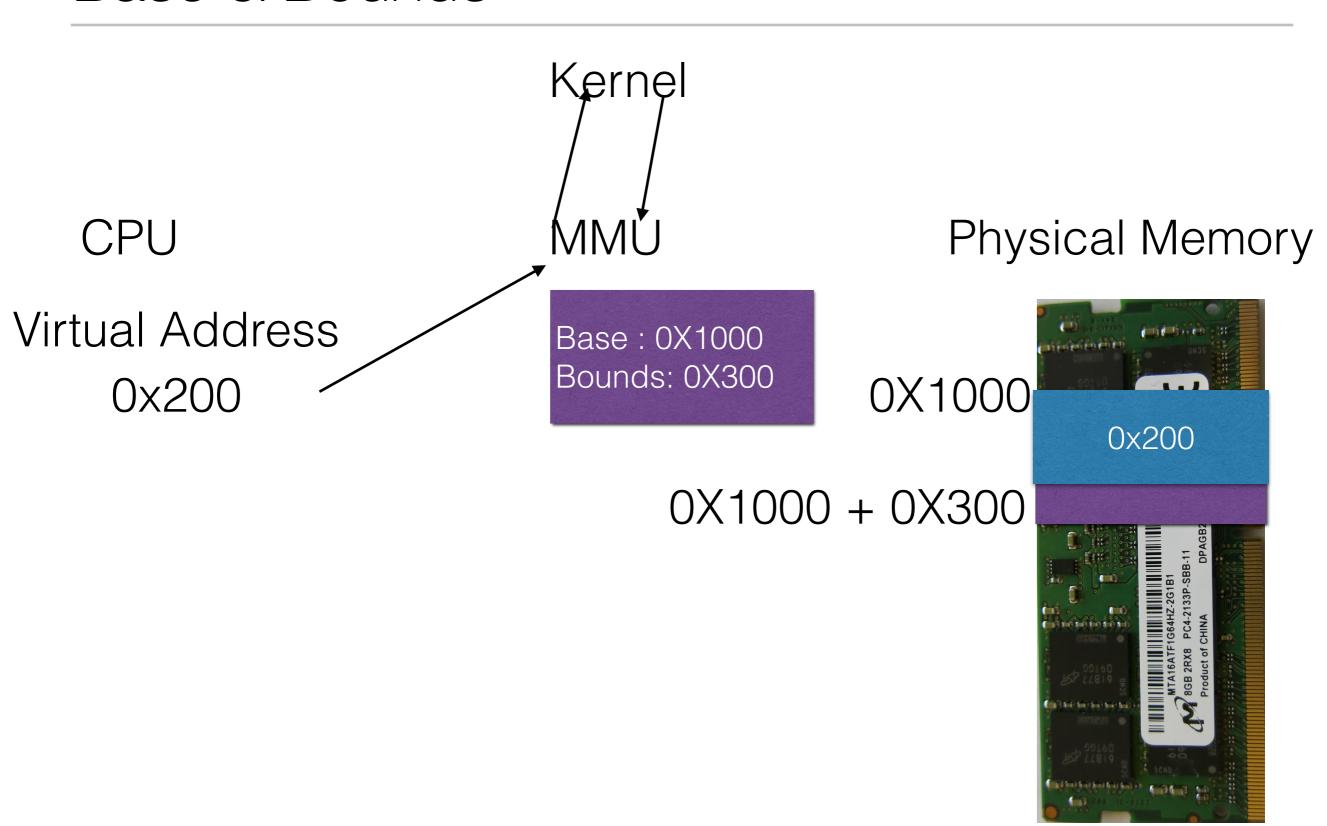

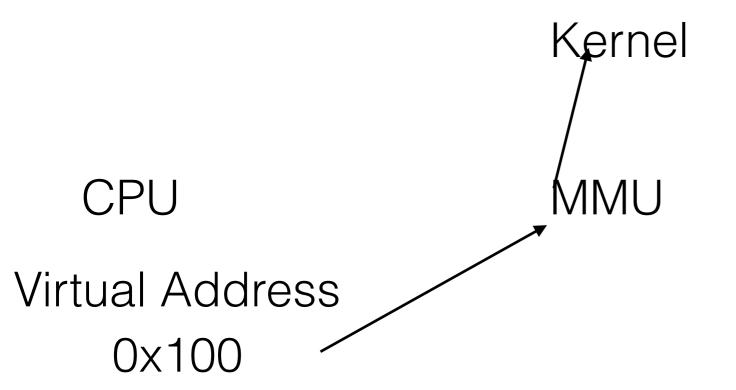

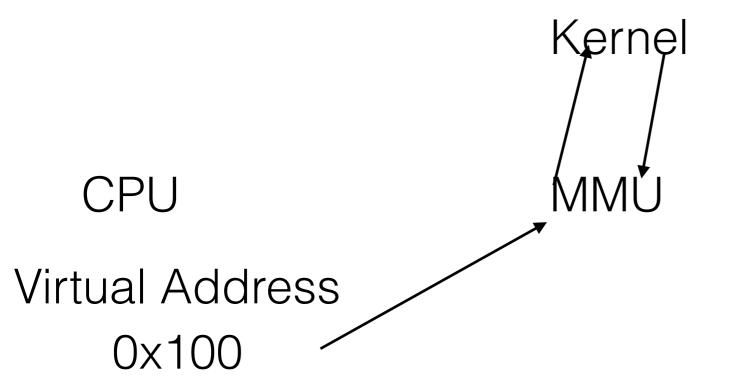

Virtual Address 0x100

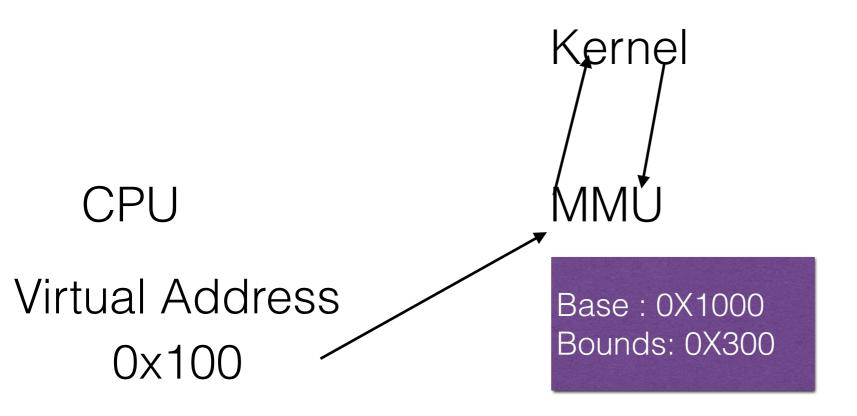

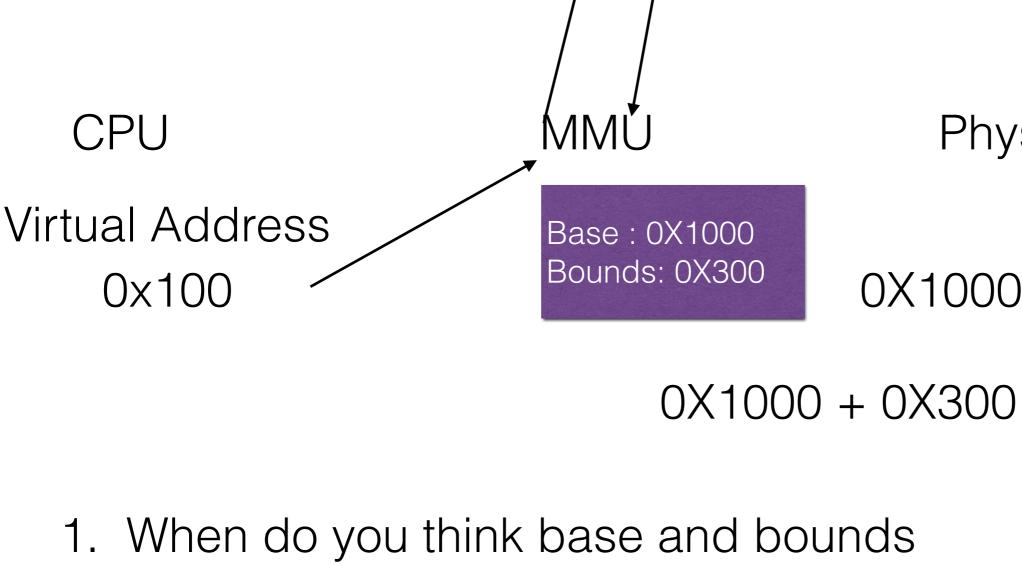

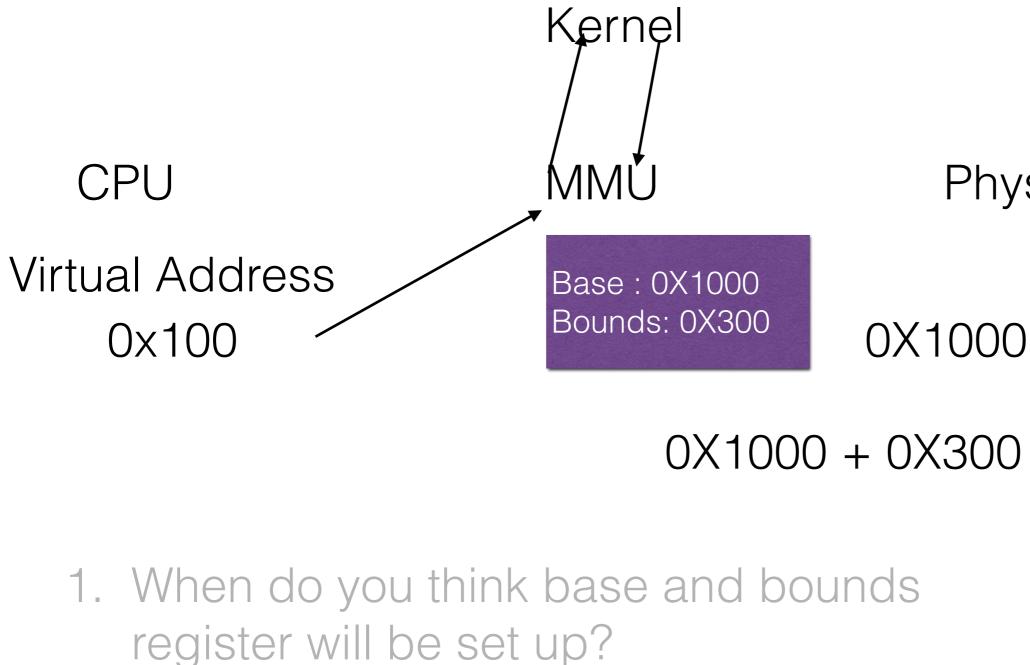

Kernel

CPU MMU

Virtual Address

0x100

CPU MMU

Virtual Address

0x100

Kernel

register will be set up?

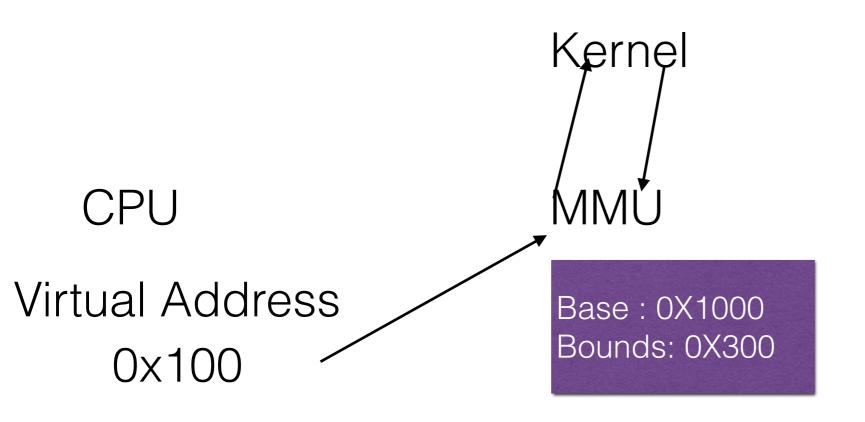

1. Base and Bound registers

- 1. Base and Bound registers

- 2. Allows:

- 1. Base and Bound registers

- 2. Allows:

- 1. Place address space anywhere in memory (not just at location 0)

- 1. Base and Bound registers

- 2. Allows:

- 1. Place address space anywhere in memory (not just at location 0)

- 2. Ensures process only accesses its own space

1. Base

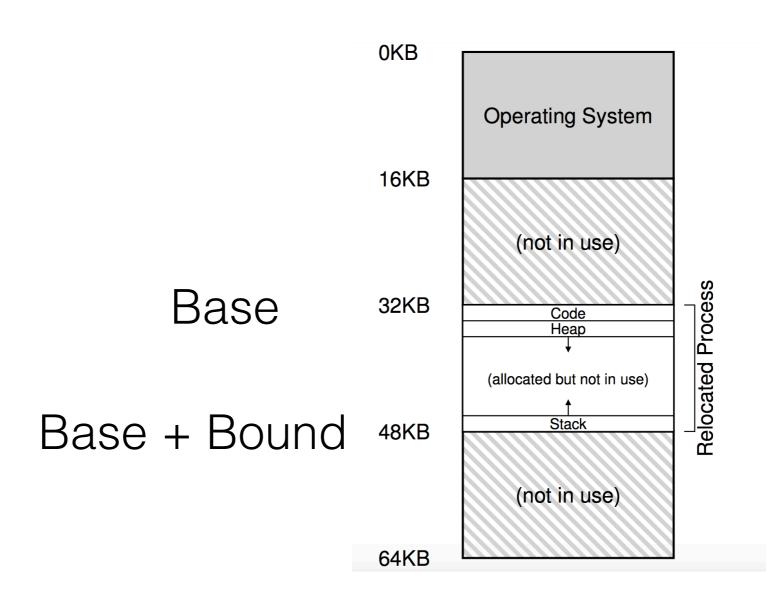

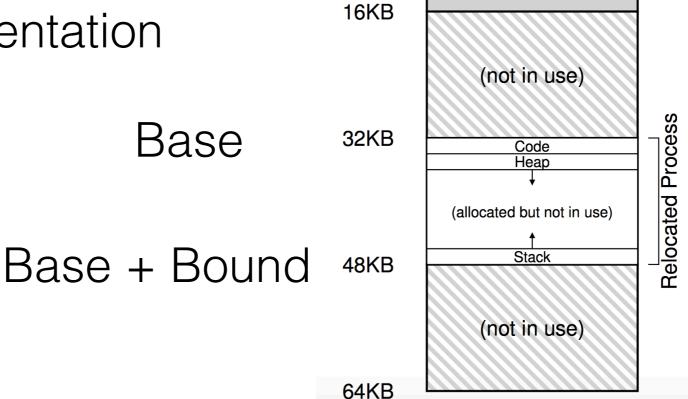

### Dynamic (Hardware-based) Relocation

#### 1. Base

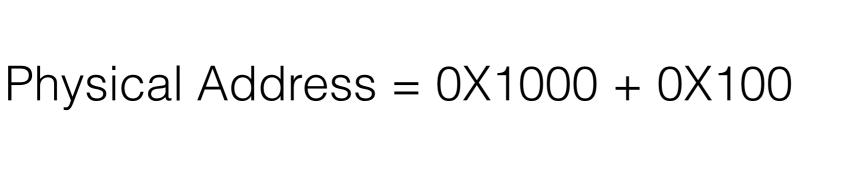

OS decides where in physical address to load the address space

## Dynamic (Hardware-based) Relocation

#### 1. Base

- 1. OS decides where in physical address to load the address space

- 2. In previous example, base is ...?

### Dynamic (Hardware-based) Relocation

#### 1. Base

- 1. OS decides where in physical address to load the address space

- 2. In previous example, base is ...?

- 3. Ans: 32 KB

128: movl 0x0(%ebx), %eax

1. PC points to 128

- 1. PC points to 128

- 2. Fetch instruction:

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. Relocation happens at runtime

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. Relocation happens at runtime

- 2. Can change the address even after creation

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. Relocation happens at runtime

- 2. Can change the address even after creation

- 3. Why would you do that? How would you do that?

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. Relocation happens at runtime

- 2. Can change the address even after creation

- 3. Why would you do that? How would you do that?

- 1. PC points to 128

- 2. Fetch instruction:

- 1. Physical Address = Base + Virtual Address = 32K + 128 = 32896

- 3. Execute load:

- 1. Data resides in Virtual Address 15 KB

- 2. Fetch data from 32 KB + 15 KB = 47 KB

- 4. Pop quiz why is it called dynamic relocation?

- 1. Relocation happens at runtime

- 2. Can change the address even after creation

- 3. Why would you do that? How would you do that?

#### Goals of OS for Memory Virtualisation

- 1. Transparency

- 1. Virtual memory is invisible to user program

- 2. Program thinks it has own private large memory

- 2. Efficiency

- 1. Not taking very long

- 2. Not taking too much space

- 3. Protection/Isolation

- 1. Protect processes from each other

#### Goals of OS for Memory Virtualisation

- 1. Transparency

- 1. Virtual memory is invisible to user program

- 2. Program thinks it has own private large memory

- 2. Efficiency

- 1. Not taking very long

- 2. Not taking too much space

- 3. Protection/Isolation

- 1. Protect processes from each other

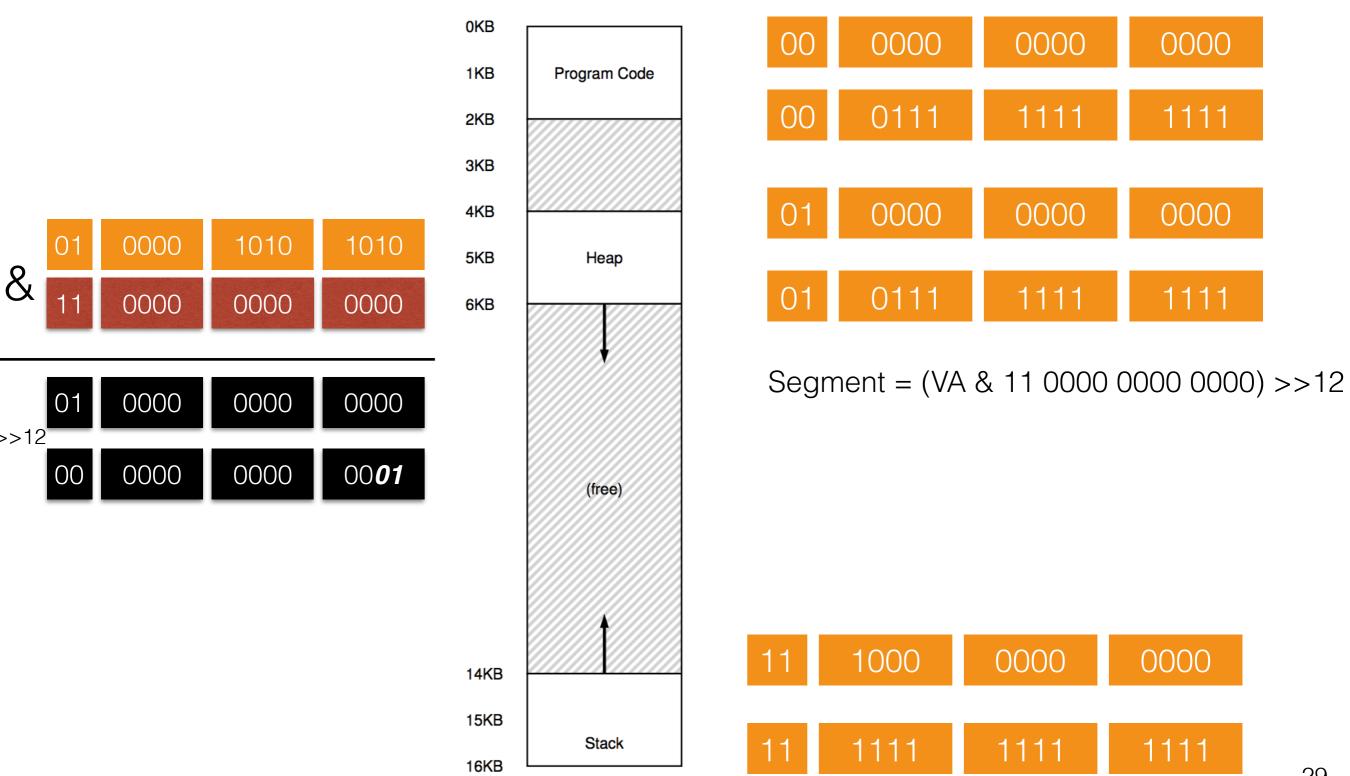

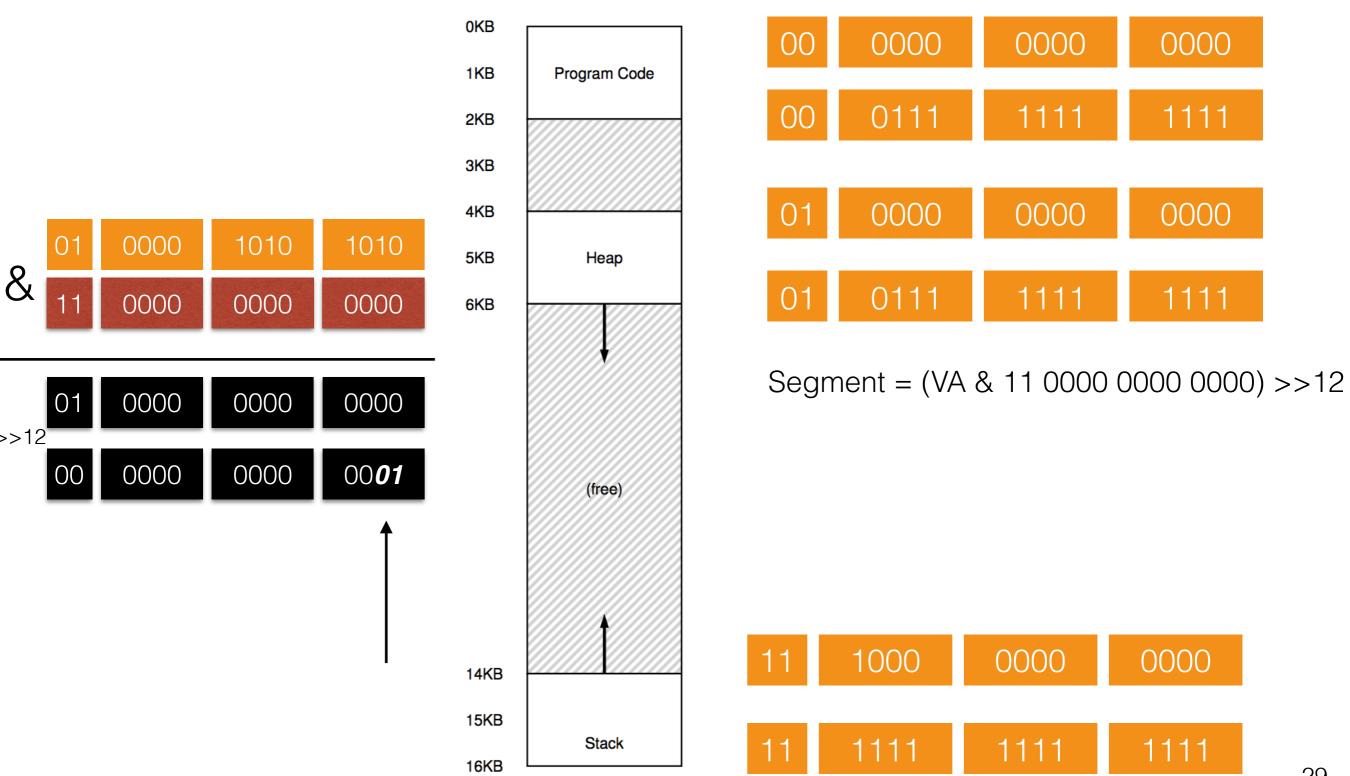

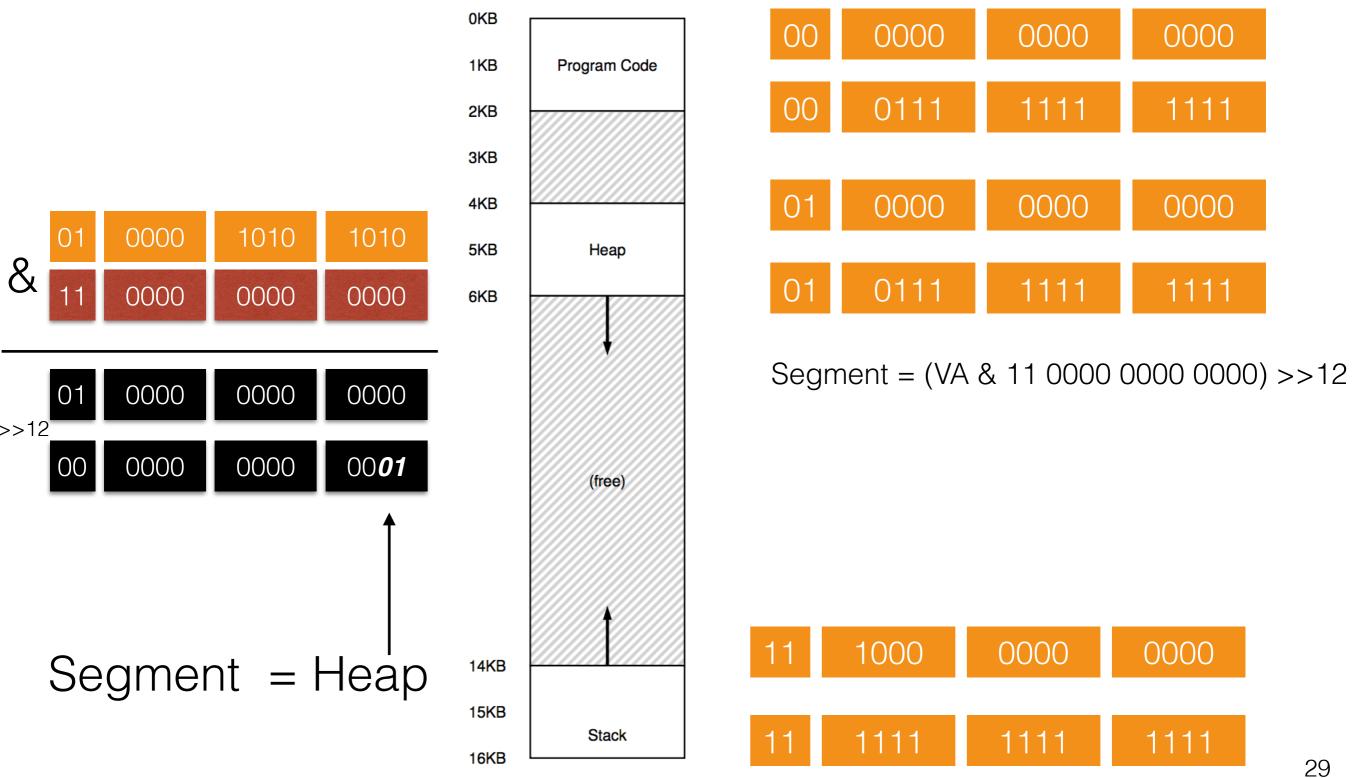

29

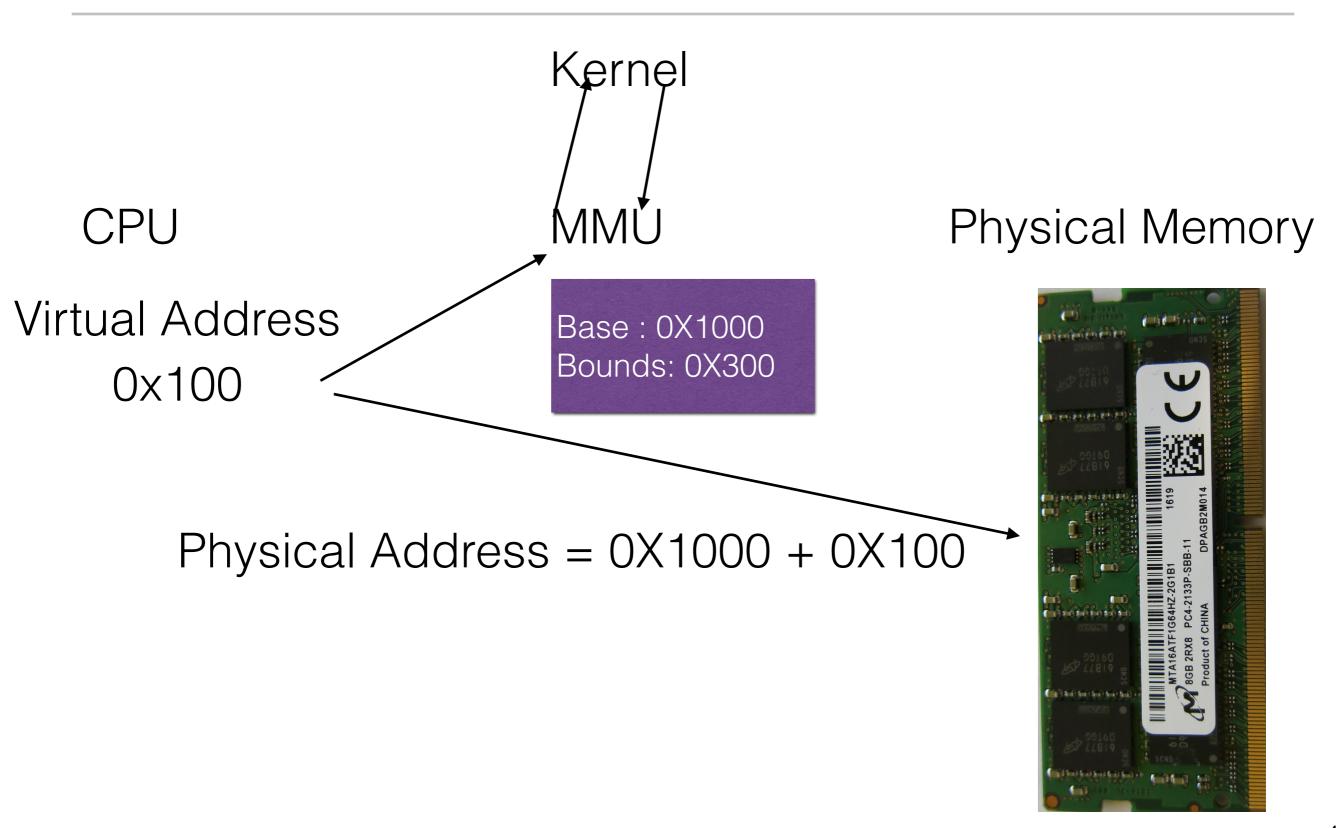

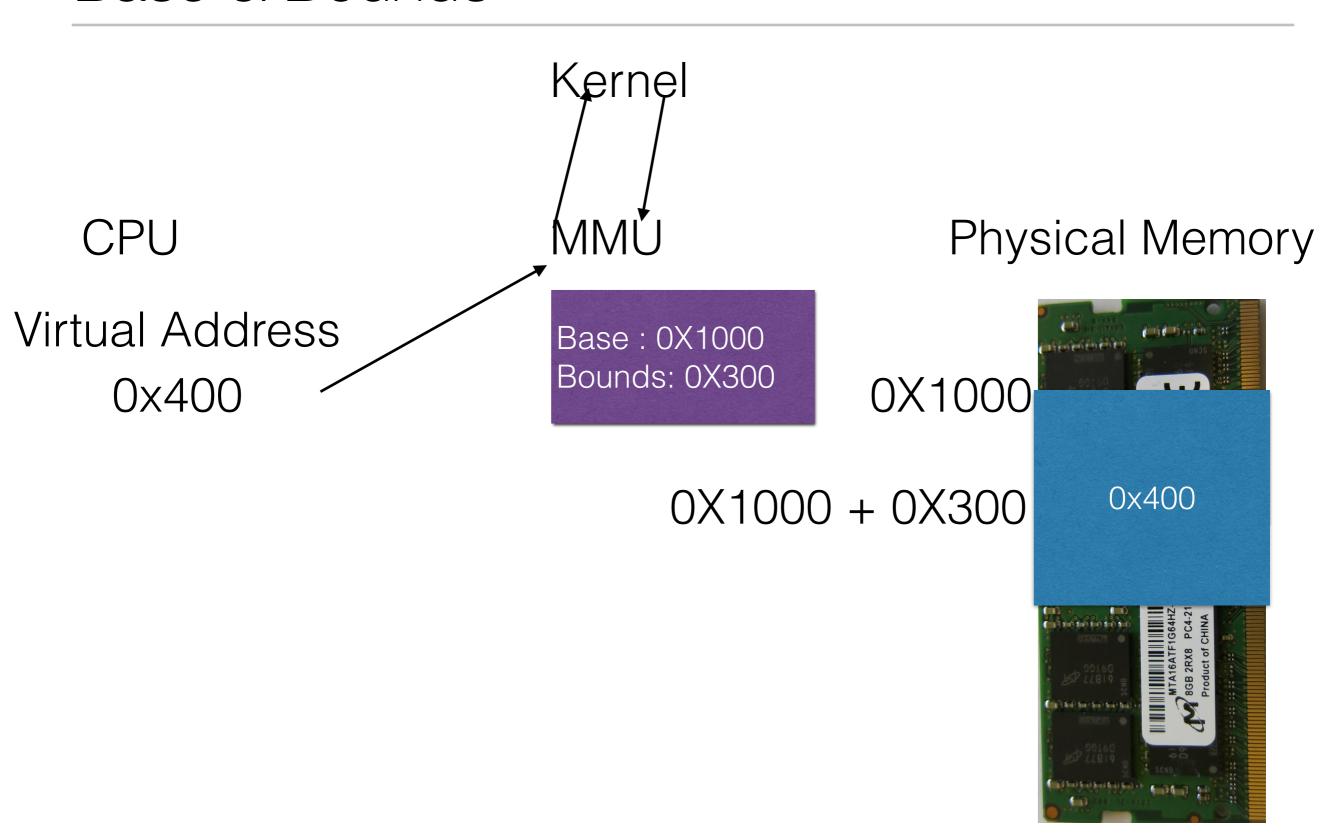

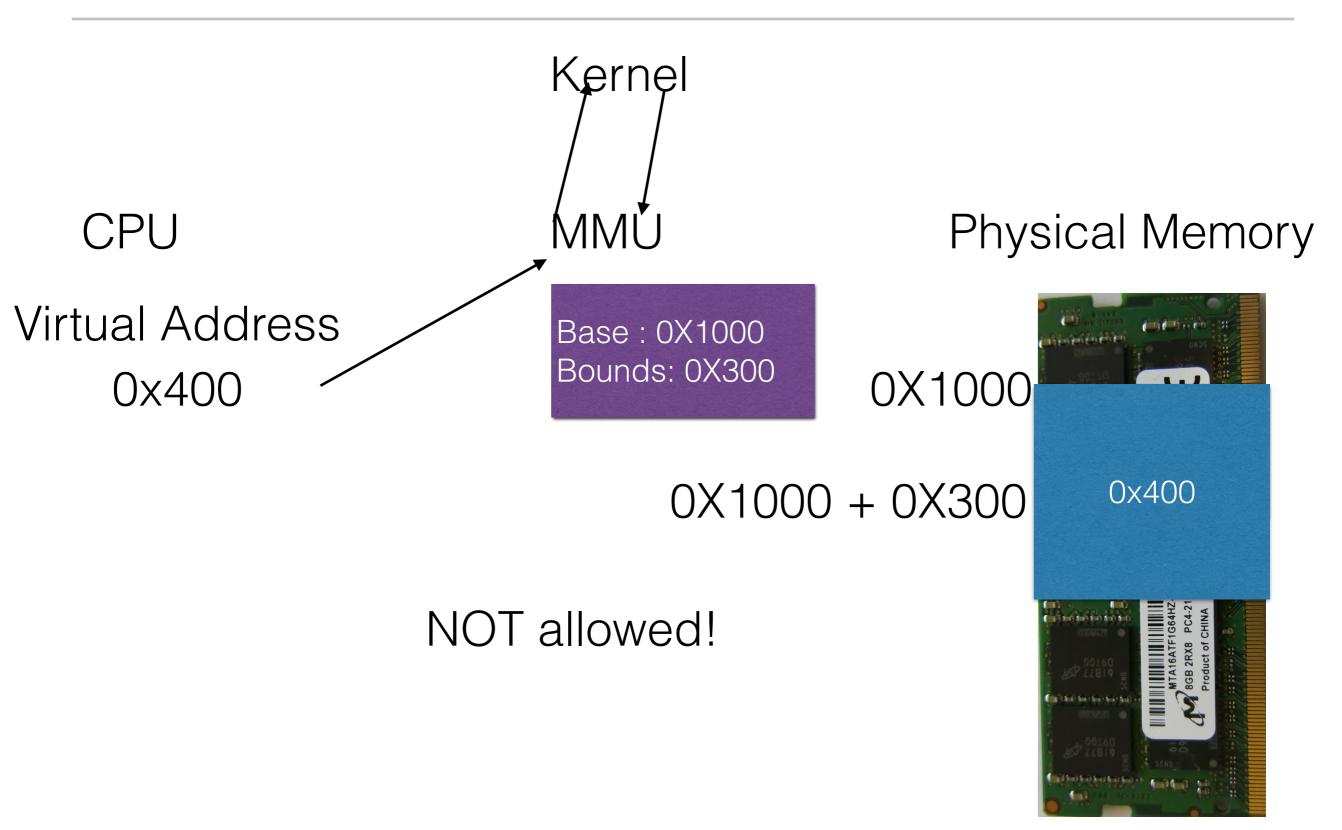

1. Checks if memory reference is within bounds

- 1. Checks if memory reference is within bounds

- 2. Pop Quiz: What's the bound in our example?

- 1. Checks if memory reference is within bounds

- 2. Pop Quiz: What's the bound in our example?

- 1. Ans: 16 KB

- 1. Checks if memory reference is within bounds

- Pop Quiz: What's the bound in our example?

Ans: 16 KB

- 3. Incorrect virtual address: Terminate!

- 1. Checks if memory reference is within bounds

- 2. Pop Quiz: What's the bound in our example?

- 1. Ans: 16 KB

- 3. Incorrect virtual address: Terminate!

- 1. Checks if memory reference is within bounds

- 2. Pop Quiz: What's the bound in our example?

- 1. Ans: 16 KB

- 3. Incorrect virtual address: Terminate!

| Hardware Requirements                  | Notes |

|----------------------------------------|-------|

| Privileged mode                        |       |

|                                        |       |

| Base/bounds registers                  |       |

|                                        |       |

| Ability to translate virtual addresses |       |

| and check if within bounds             |       |

| Privileged instruction(s) to           | _     |

| update base/bounds                     |       |

| Privileged instruction(s) to register  |       |

| exception handlers                     |       |

| Ability to raise exceptions            | _     |

|                                        |       |

| Hardware Requirements                  | Notes                                 |

|----------------------------------------|---------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes |

|                                        | from executing privileged operations  |

| Base/bounds registers                  |                                       |

|                                        |                                       |

| Ability to translate virtual addresses |                                       |

| and check if within bounds             |                                       |

| Privileged instruction(s) to           |                                       |

| update base/bounds                     |                                       |

| Privileged instruction(s) to register  |                                       |

| exception handlers                     |                                       |

| Ability to raise exceptions            |                                       |

| j                                      |                                       |

| Hardware Requirements                  | Notes                                     |

|----------------------------------------|-------------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes     |

|                                        | from executing privileged operations      |

| Base/bounds registers                  | Need pair of registers per CPU to support |

|                                        | address translation and bounds checks     |

| Ability to translate virtual addresses |                                           |

| and check if within bounds             |                                           |

| Privileged instruction(s) to           |                                           |

| update base/bounds                     |                                           |

| Privileged instruction(s) to register  |                                           |

| exception handlers                     |                                           |

| Ability to raise exceptions            | <del>_</del>                              |

|                                        |                                           |

| Hardware Requirements                  | Notes                                     |

|----------------------------------------|-------------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes     |

|                                        | from executing privileged operations      |

| Base/bounds registers                  | Need pair of registers per CPU to support |

|                                        | address translation and bounds checks     |

| Ability to translate virtual addresses | Circuitry to do translations and check    |

| and check if within bounds             | limits; in this case, quite simple        |

| Privileged instruction(s) to           | <del>_</del>                              |

| update base/bounds                     |                                           |

| Privileged instruction(s) to register  |                                           |

| exception handlers                     |                                           |

| Ability to raise exceptions            | <del>_</del>                              |

|                                        |                                           |

| Hardware Requirements                  | Notes                                     |

|----------------------------------------|-------------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes     |

|                                        | from executing privileged operations      |

| Base/bounds registers                  | Need pair of registers per CPU to support |

|                                        | address translation and bounds checks     |

| Ability to translate virtual addresses | Circuitry to do translations and check    |

| and check if within bounds             | limits; in this case, quite simple        |

| Privileged instruction(s) to           | OS must be able to set these values       |

| update base/bounds                     | before letting a user program run         |

| Privileged instruction(s) to register  |                                           |

| exception handlers                     |                                           |

| Ability to raise exceptions            |                                           |

|                                        |                                           |

| Hardware Requirements                  | Notes                                     |

|----------------------------------------|-------------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes     |

|                                        | from executing privileged operations      |

| Base/bounds registers                  | Need pair of registers per CPU to support |

|                                        | address translation and bounds checks     |

| Ability to translate virtual addresses | Circuitry to do translations and check    |

| and check if within bounds             | limits; in this case, quite simple        |

| Privileged instruction(s) to           | OS must be able to set these values       |

| update base/bounds                     | before letting a user program run         |

| Privileged instruction(s) to register  | OS must be able to tell hardware what     |

| exception handlers                     | code to run if exception occurs           |

| Ability to raise exceptions            |                                           |

| Hardware Requirements                  | Notes                                     |

|----------------------------------------|-------------------------------------------|

| Privileged mode                        | Needed to prevent user-mode processes     |

|                                        | from executing privileged operations      |

| Base/bounds registers                  | Need pair of registers per CPU to support |

|                                        | address translation and bounds checks     |

| Ability to translate virtual addresses | Circuitry to do translations and check    |

| and check if within bounds             | limits; in this case, quite simple        |

| Privileged instruction(s) to           | OS must be able to set these values       |

| update base/bounds                     | before letting a user program run         |

| Privileged instruction(s) to register  | OS must be able to tell hardware what     |

| exception handlers                     | code to run if exception occurs           |

| Ability to raise exceptions            | When processes try to access privileged   |

|                                        | instructions or out-of-bounds memory      |

1. Memory Management:

- 1. Memory Management:

- 1. Allocate memory for new processes

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 3. Manage memory via free list

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 3. Manage memory via free list

- 2. Base/Bound management:

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 3. Manage memory via free list

- 2. Base/Bound management:

- 1. Set base/bound upon context switch

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 3. Manage memory via free list

- 2. Base/Bound management:

- 1. Set base/bound upon context switch

- 3. Exception handling:

- 1. Memory Management:

- 1. Allocate memory for new processes

- 2. Reclaim memory from terminated process

- 3. Manage memory via free list

- 2. Base/Bound management:

- 1. Set base/bound upon context switch

- 3. Exception handling:

- 1. Terminate offending process

1. Simple: Hardware only needs to know base & bounds

- 1. Simple: Hardware only needs to know base & bounds

- 2. Relatively fast:

- 1. Simple: Hardware only needs to know base & bounds

- 2. Relatively fast:

- 1. Protection: 1 comparison (bound)

- 1. Simple: Hardware only needs to know base & bounds

- 2. Relatively fast:

- 1. Protection: 1 comparison (bound)

- 2. Translation: 1 addition

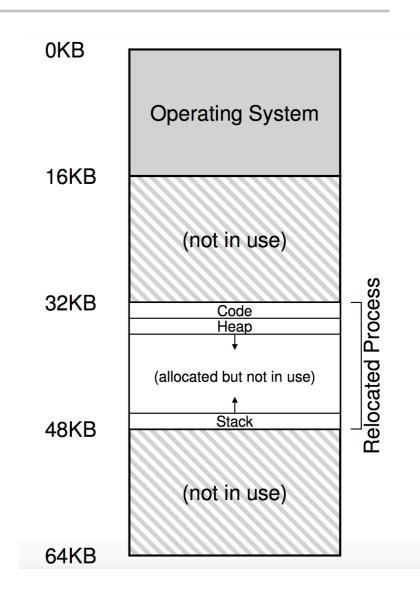

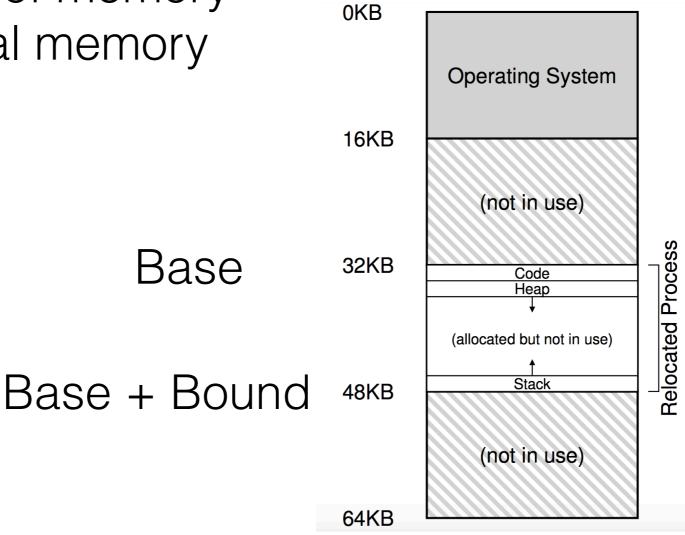

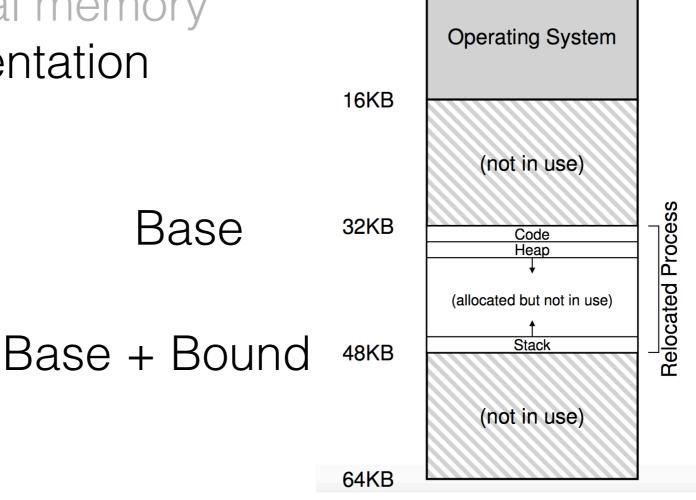

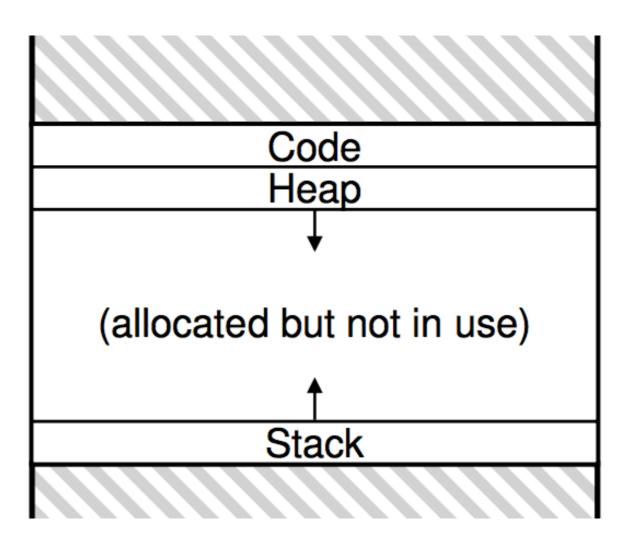

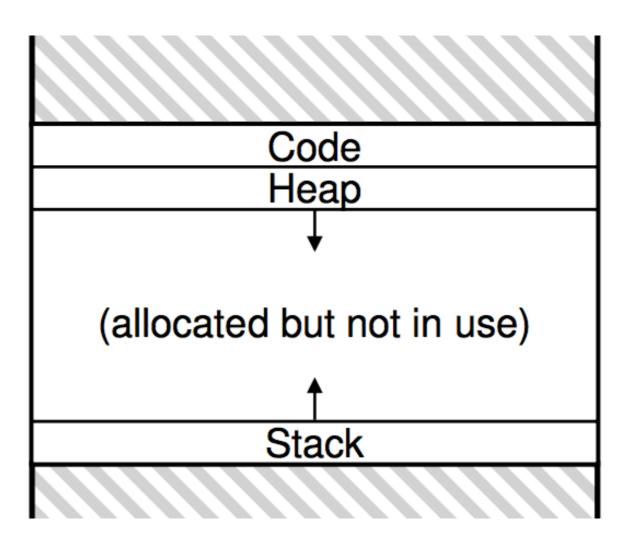

1. Contiguous block of memory needed in physical memory

- 1. Contiguous block of memory needed in physical memory

- 1. Internal fragmentation

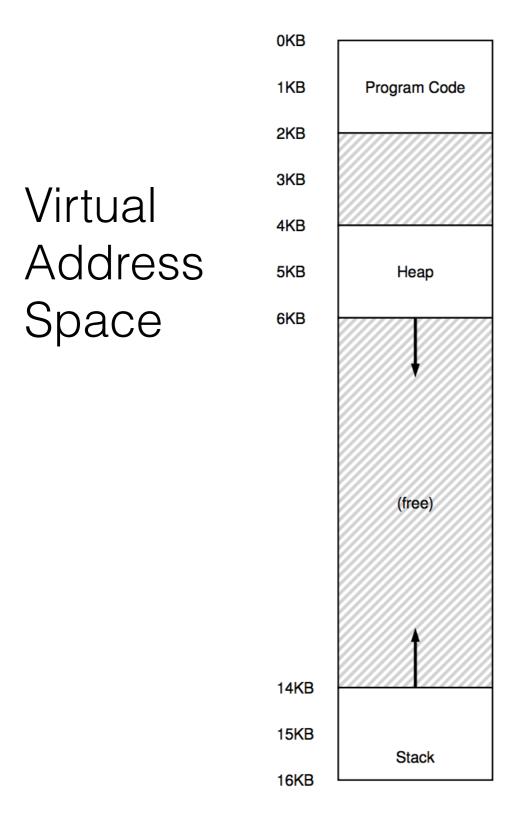

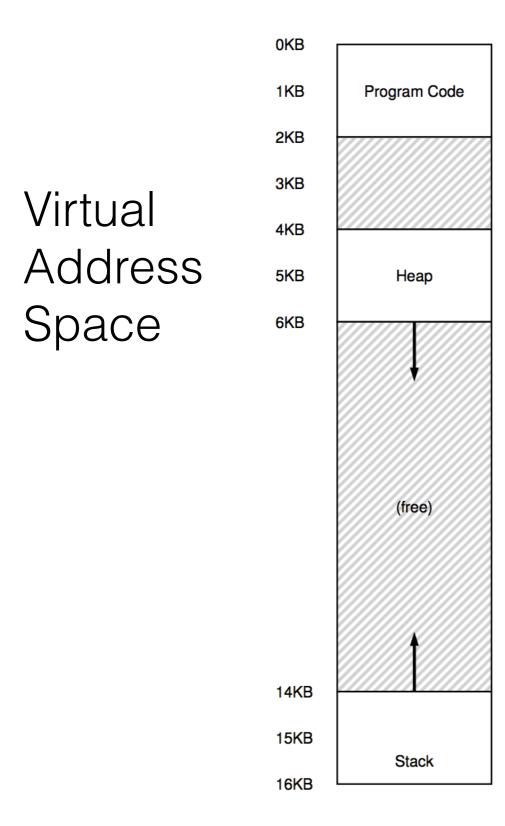

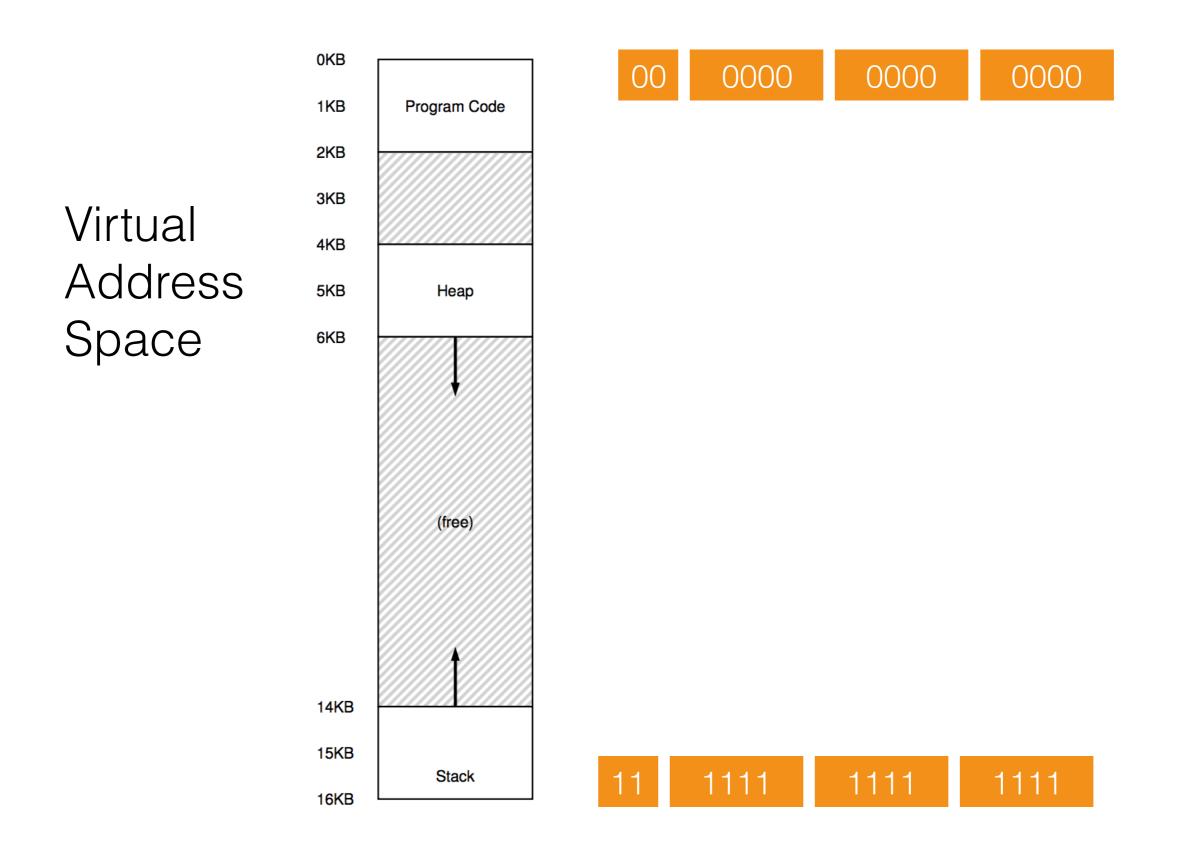

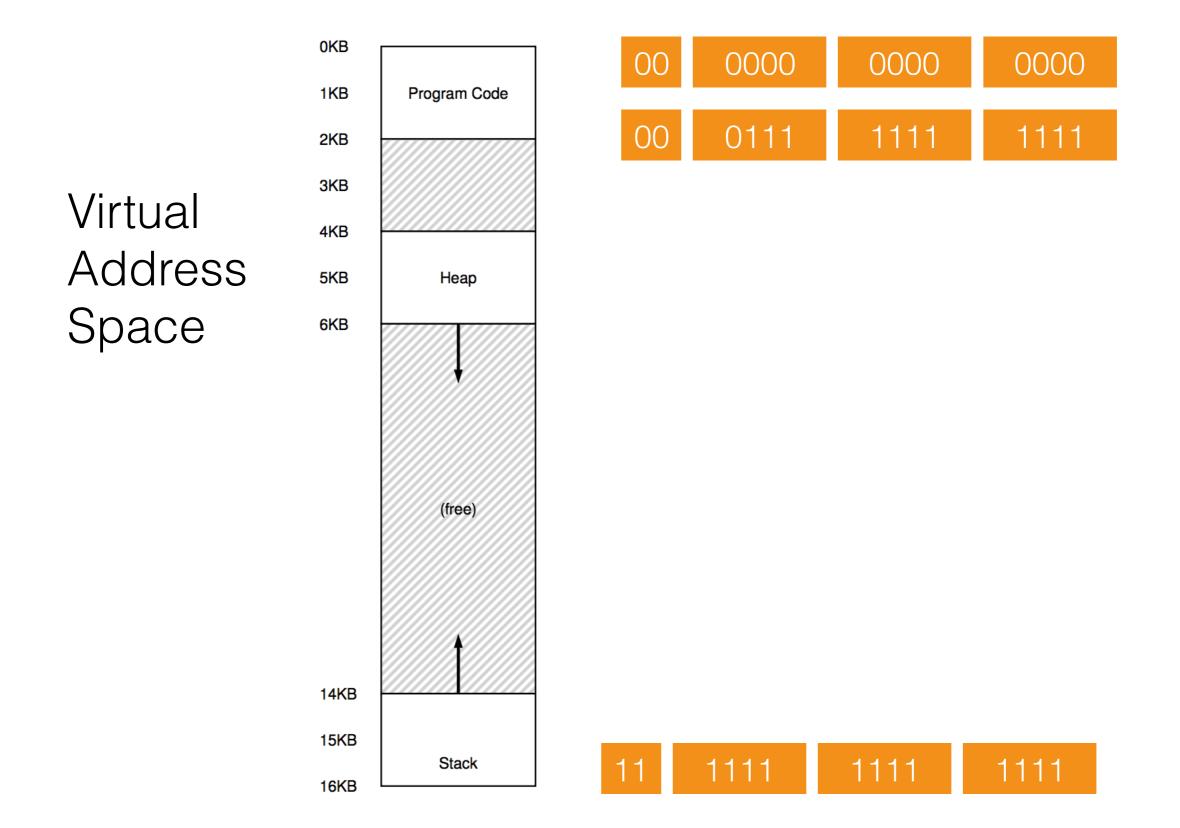

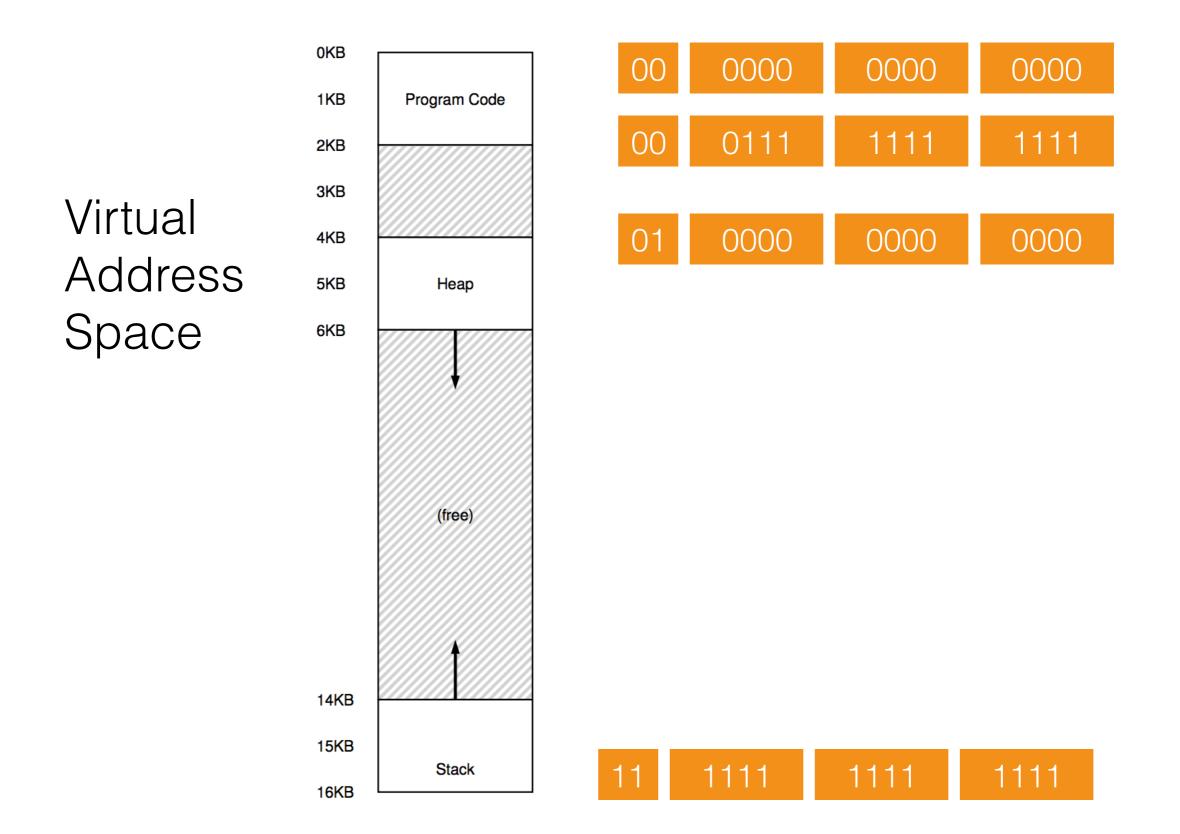

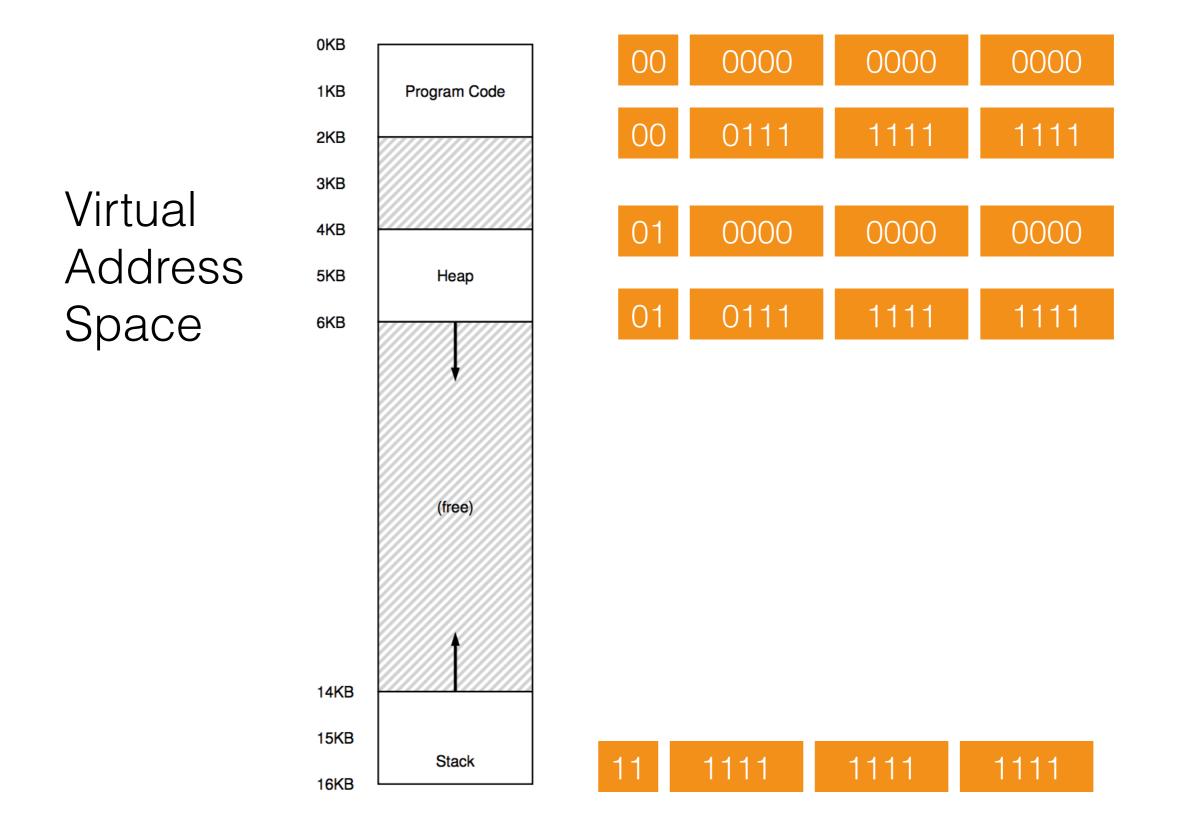

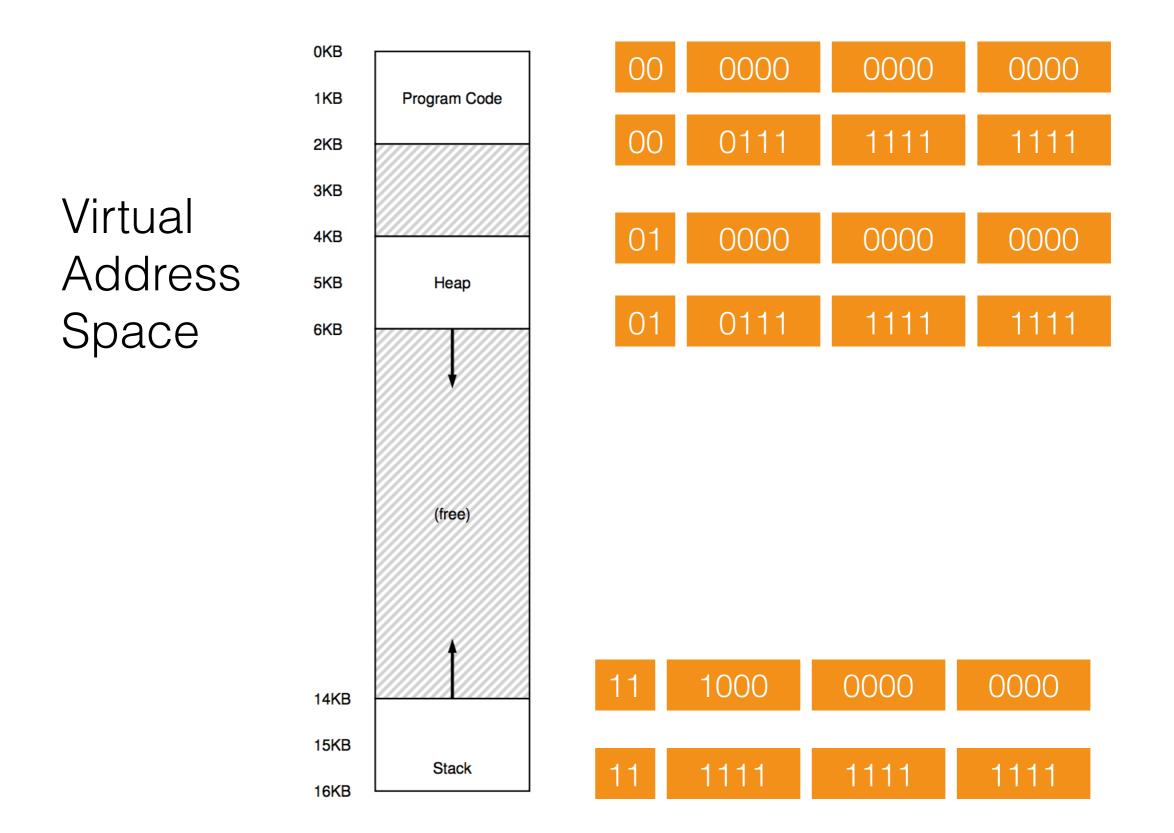

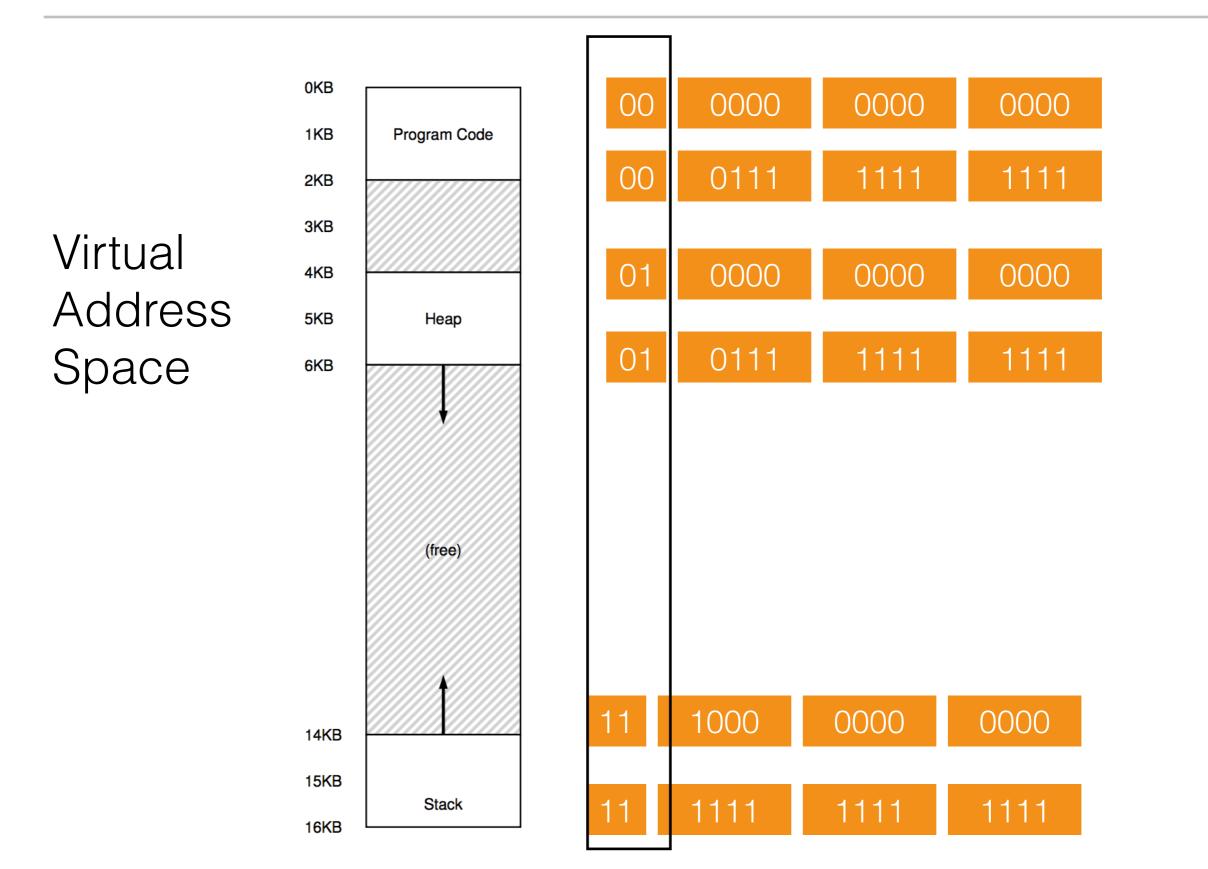

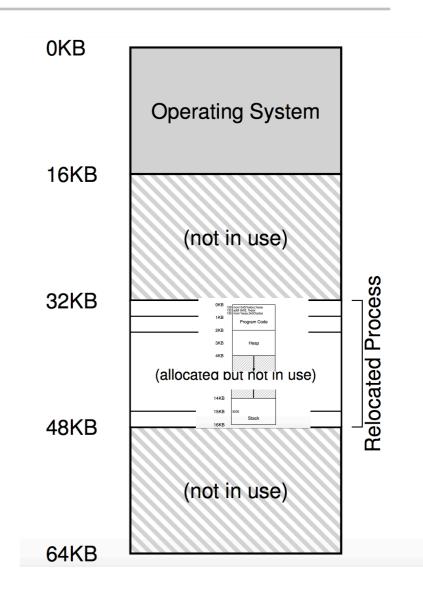

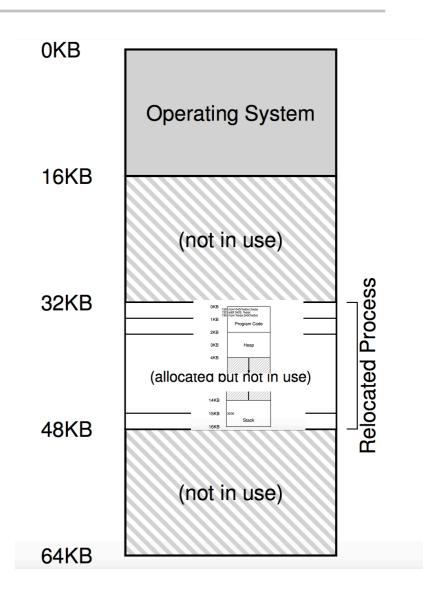

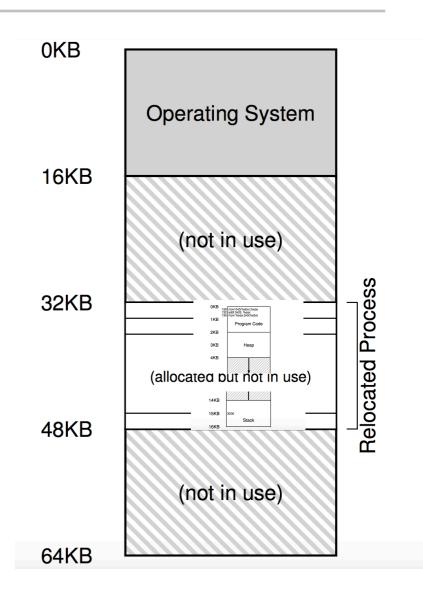

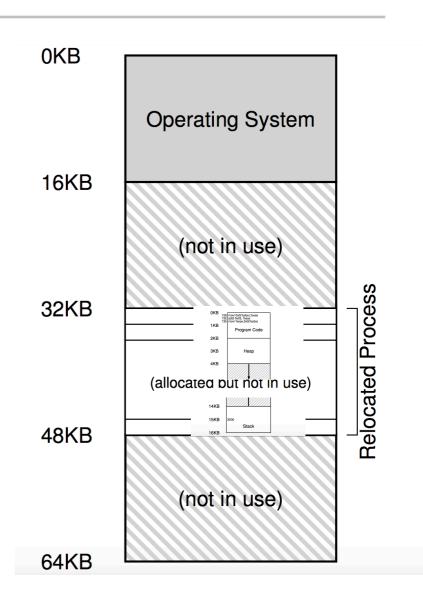

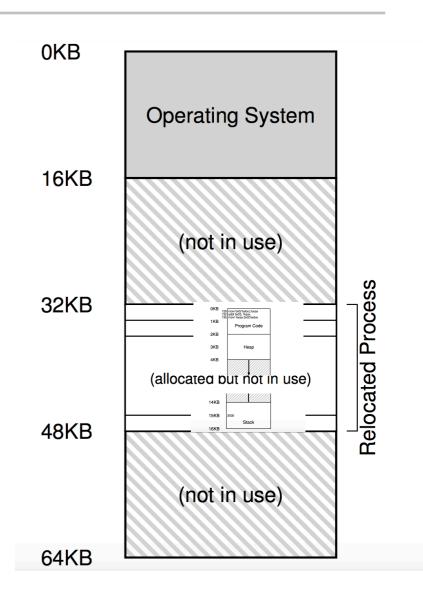

0KB

- 1. Contiguous block of memory needed in physical memory

- 1. Internal fragmentation

- 2. External fragmentation

0KB

**Operating System**

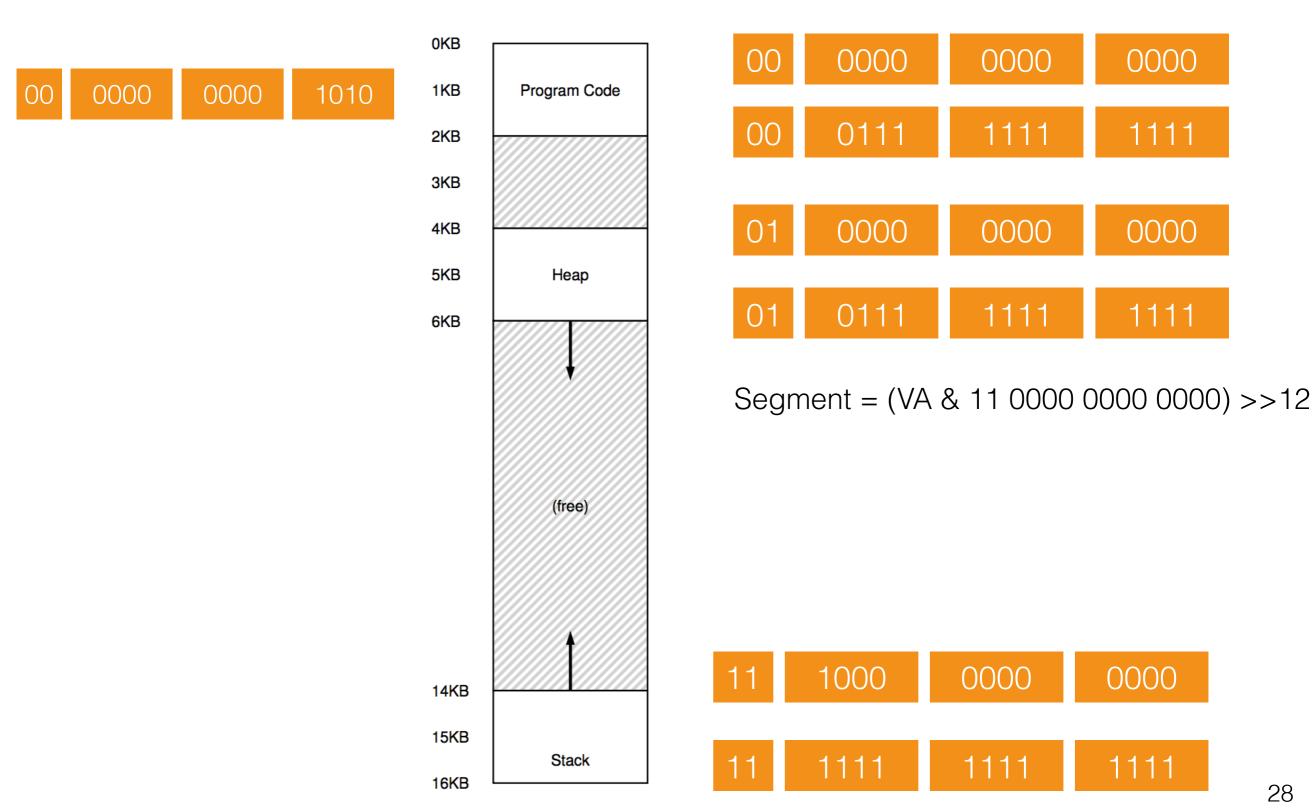

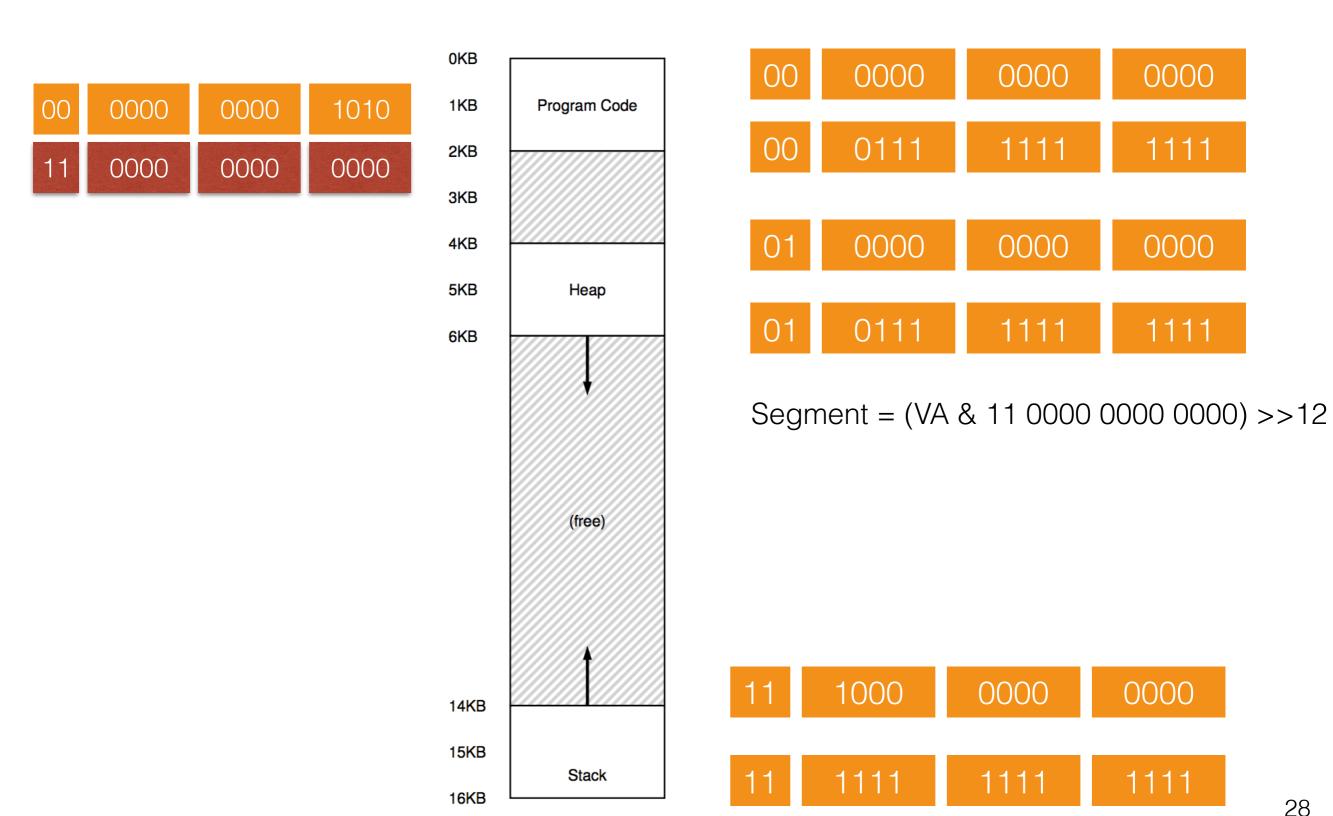

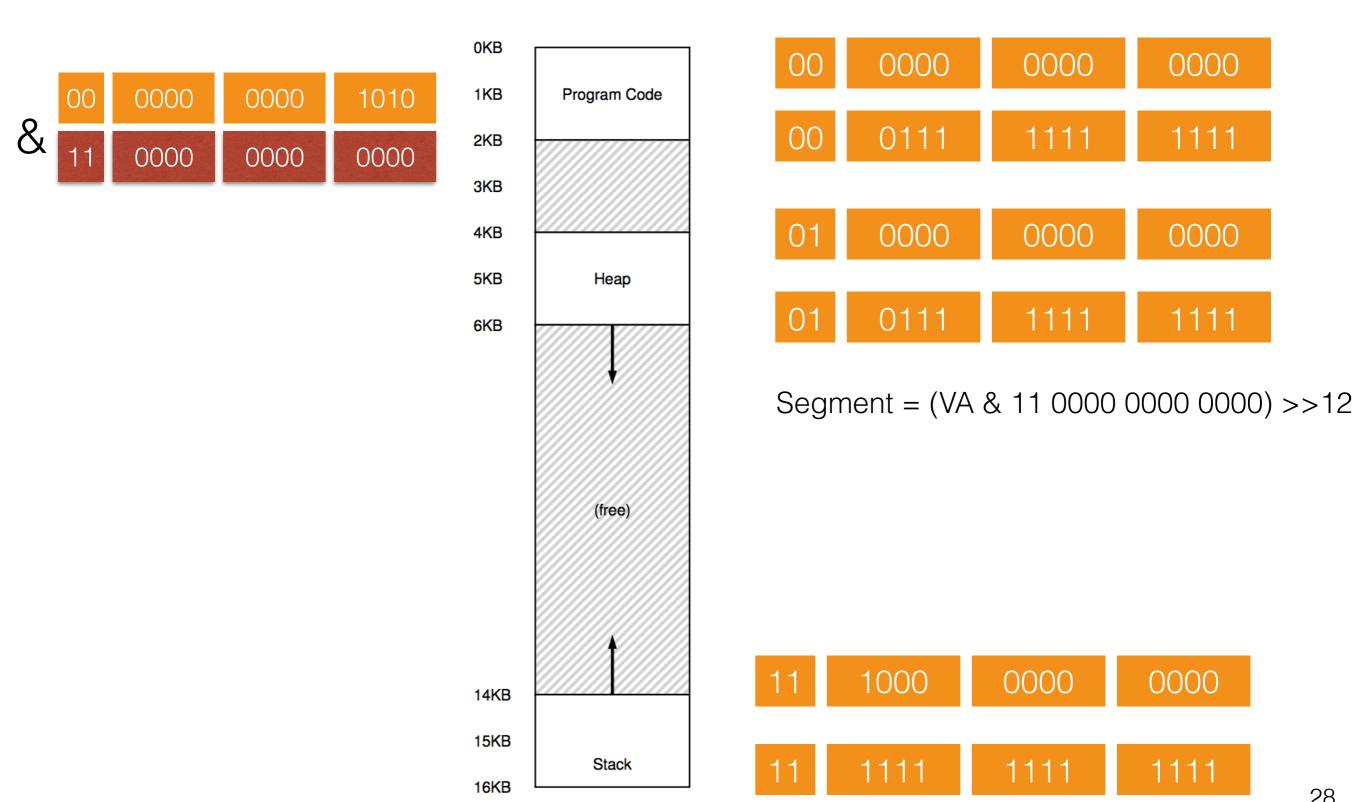

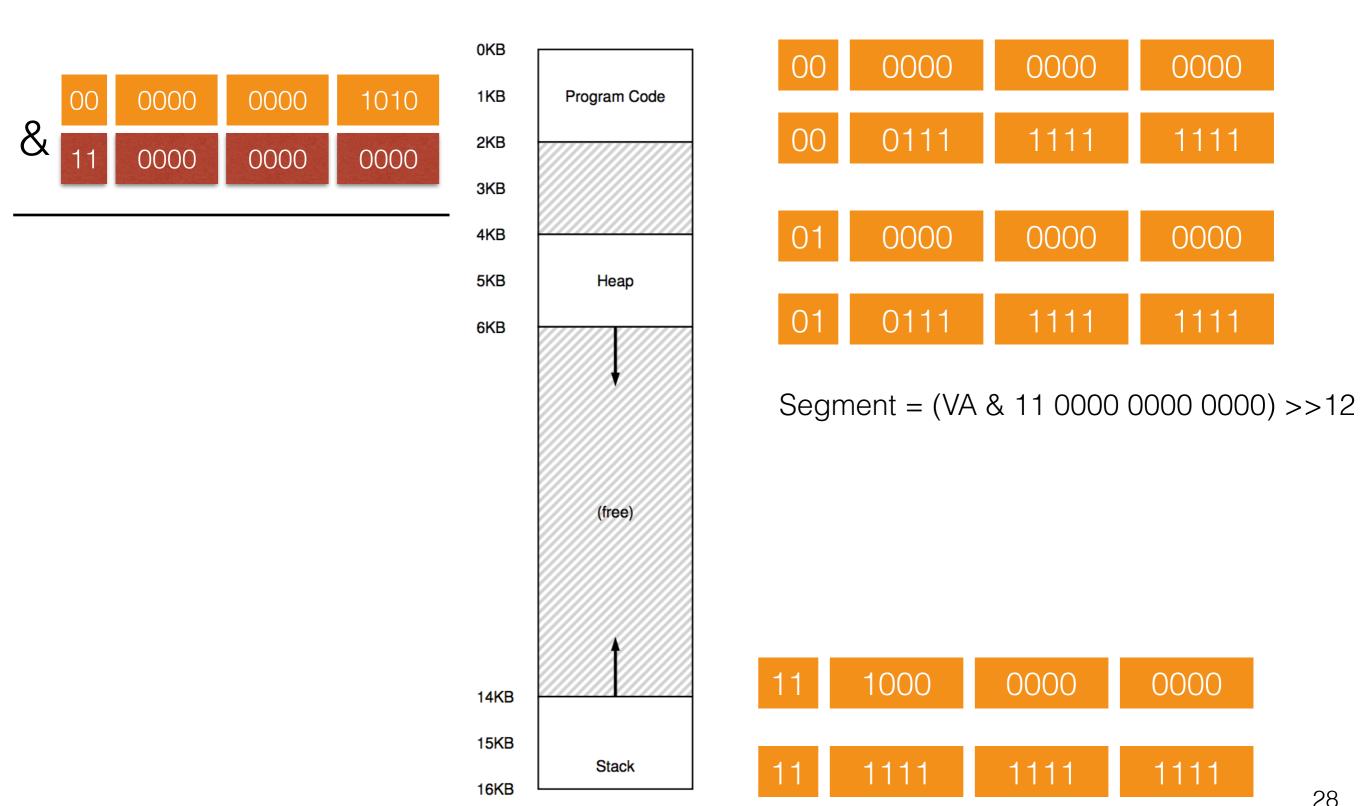

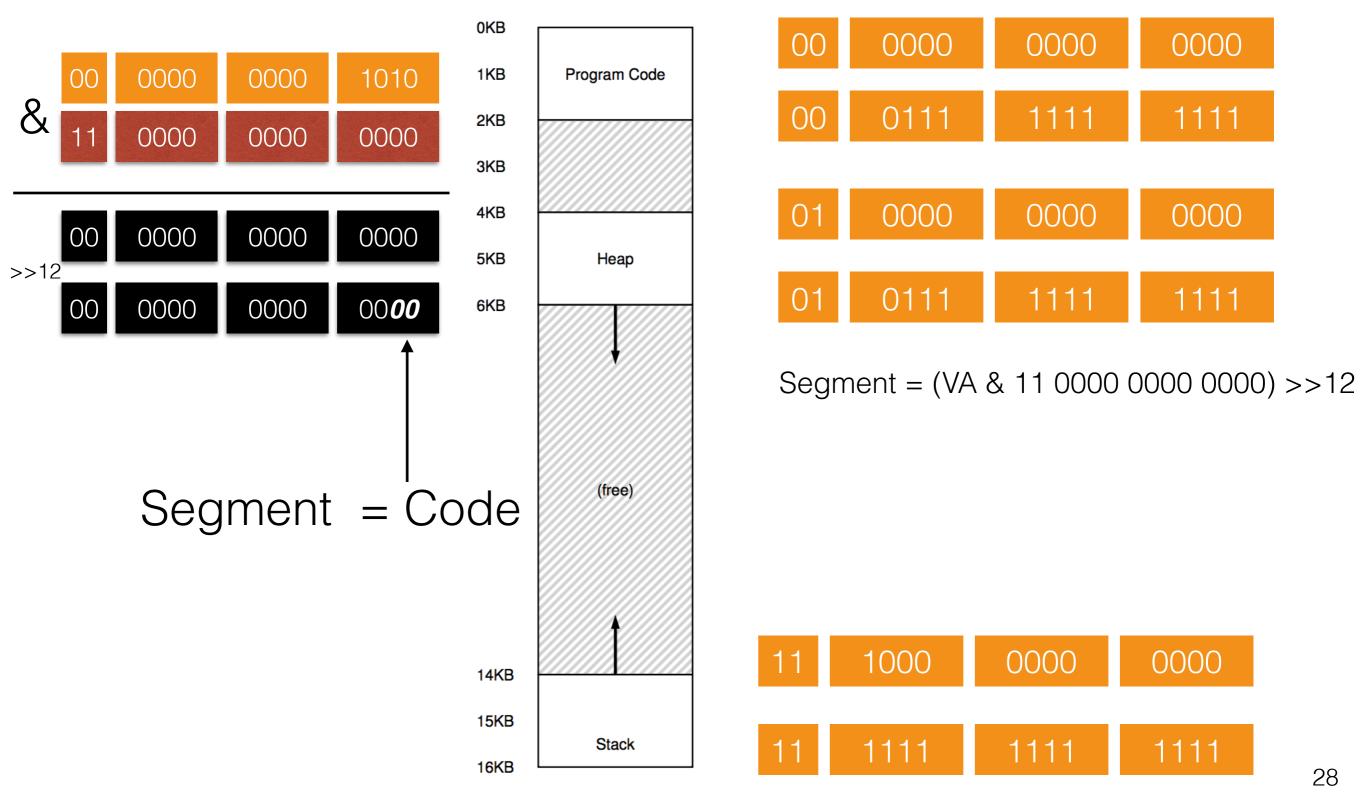

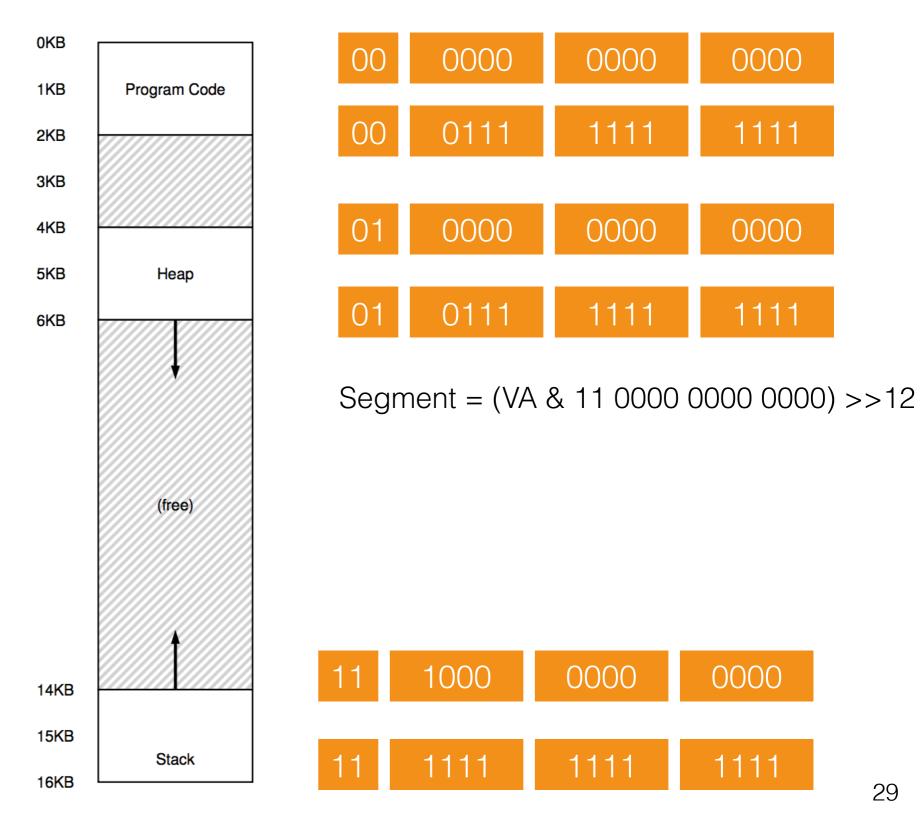

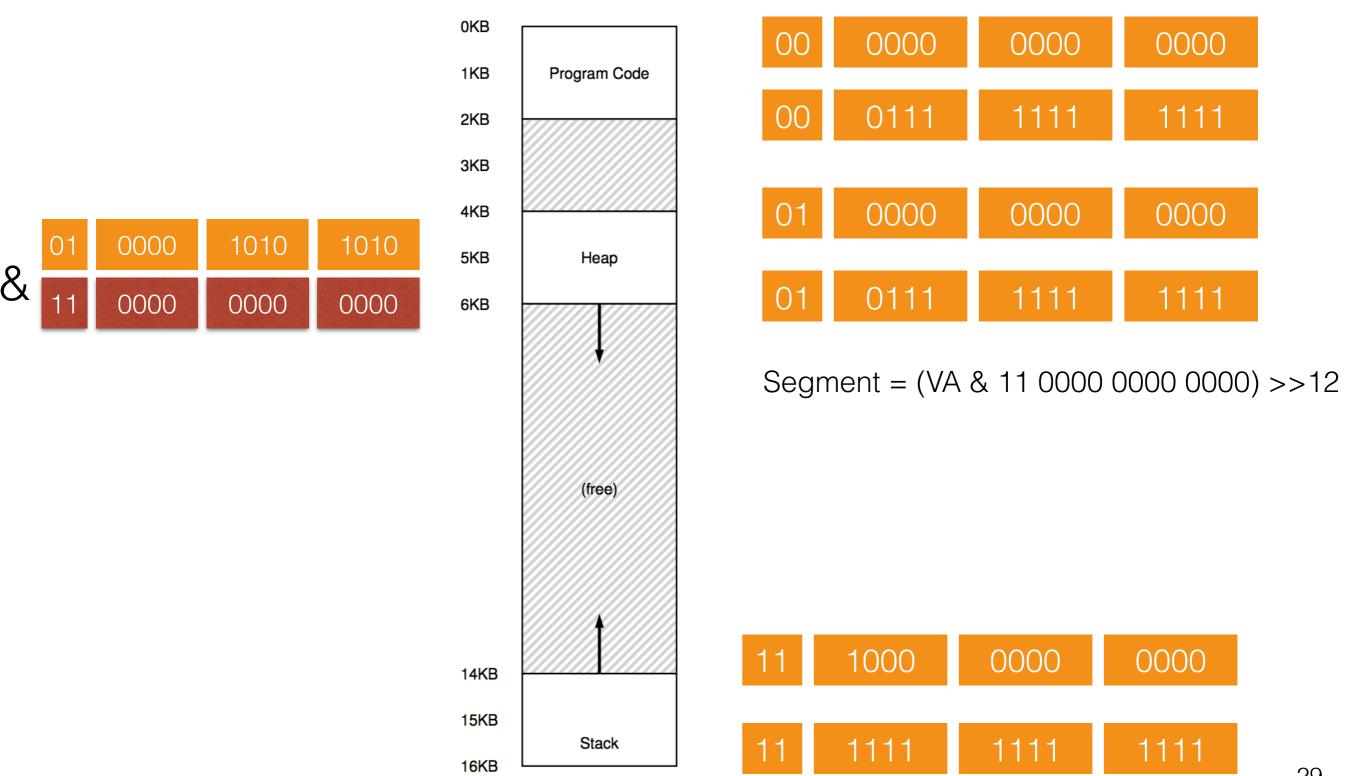

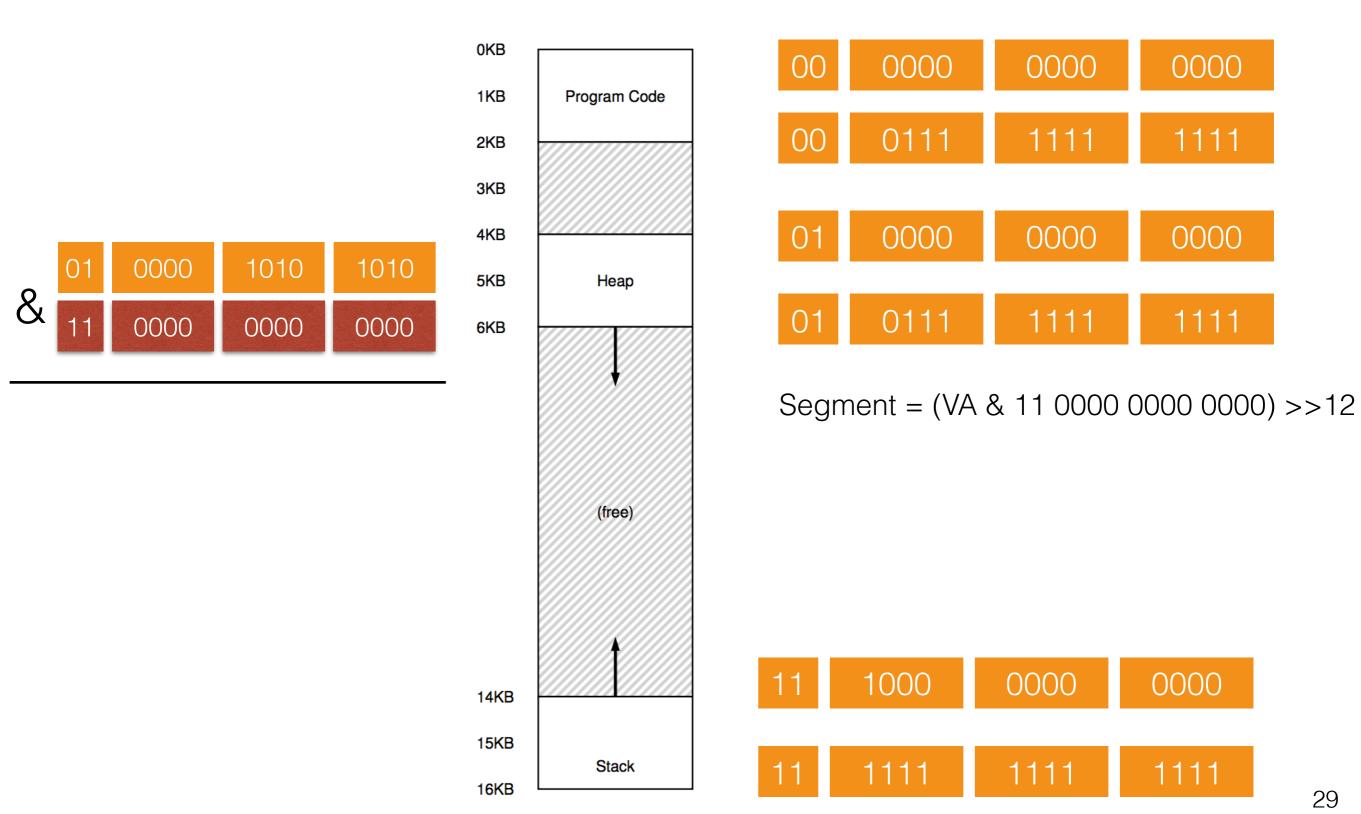

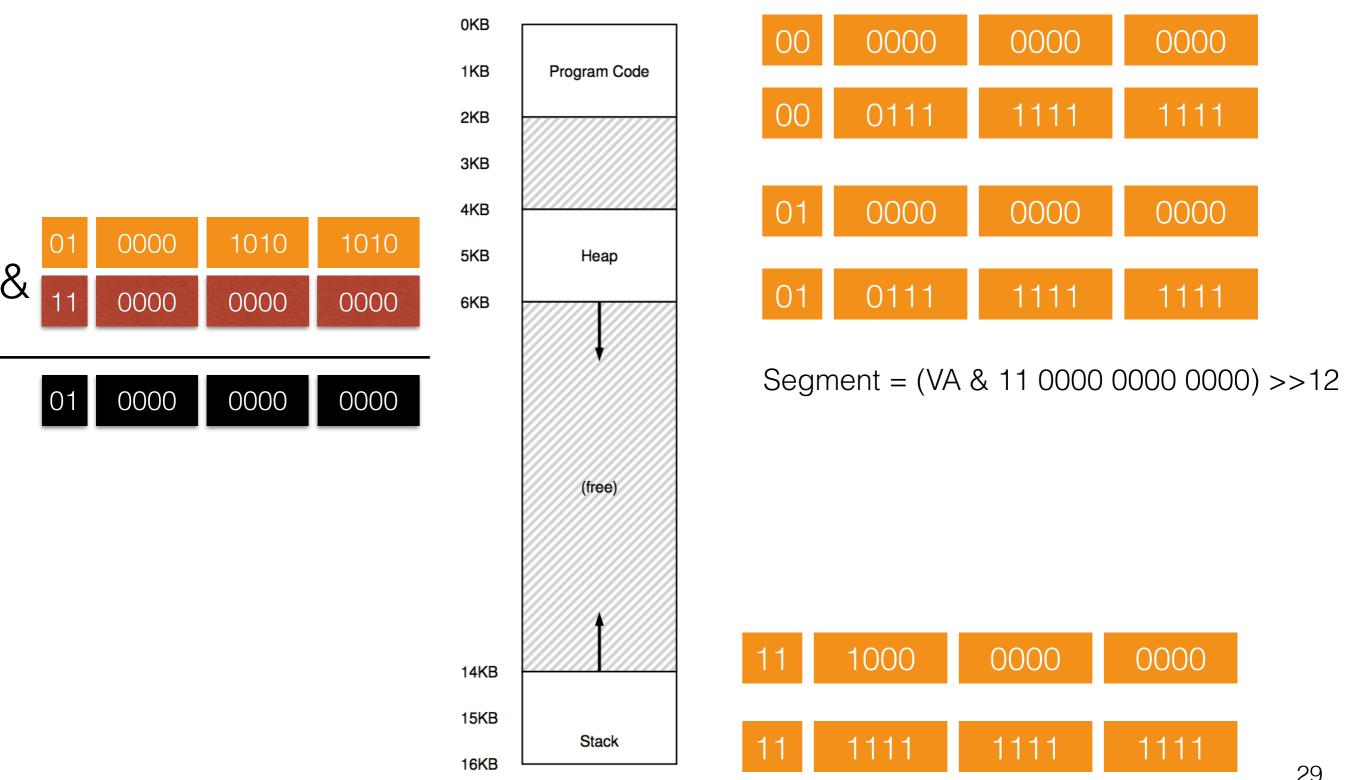

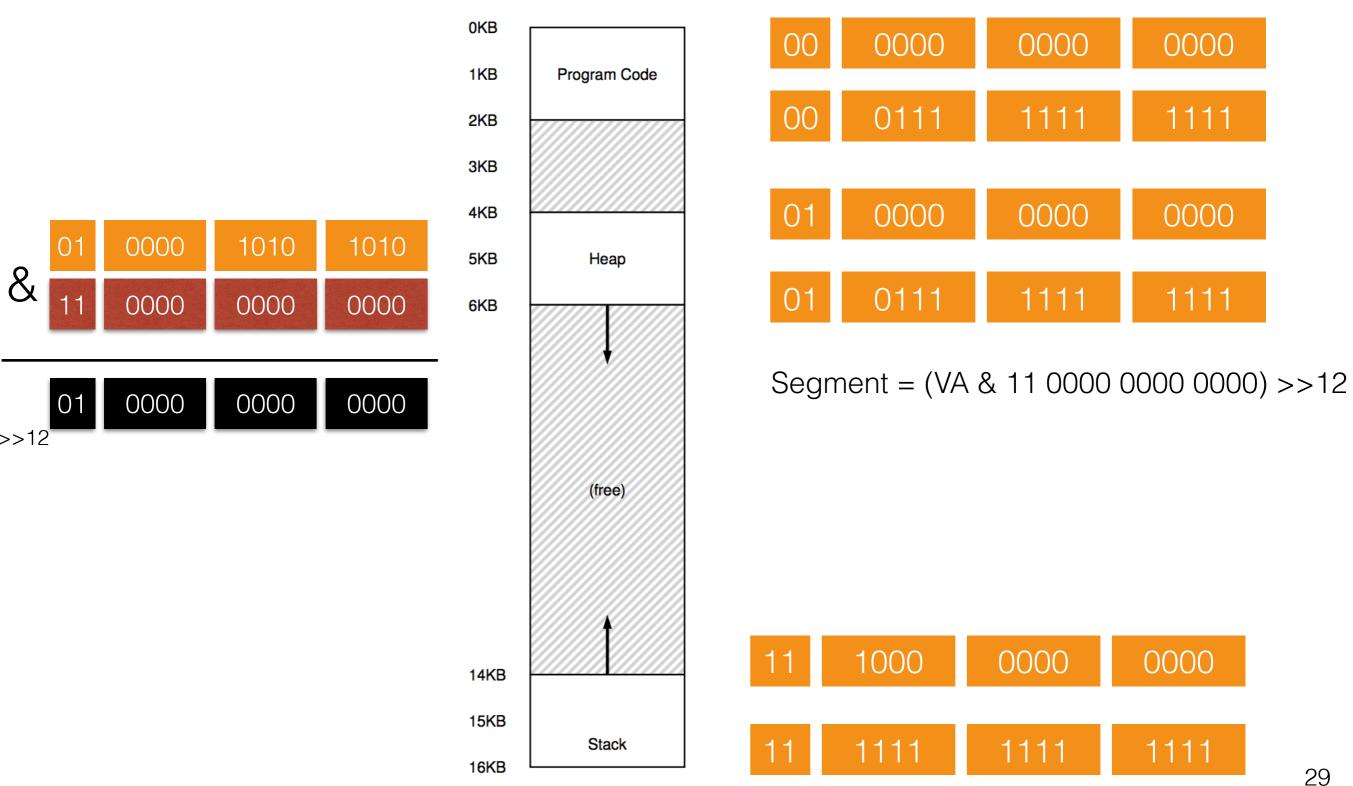

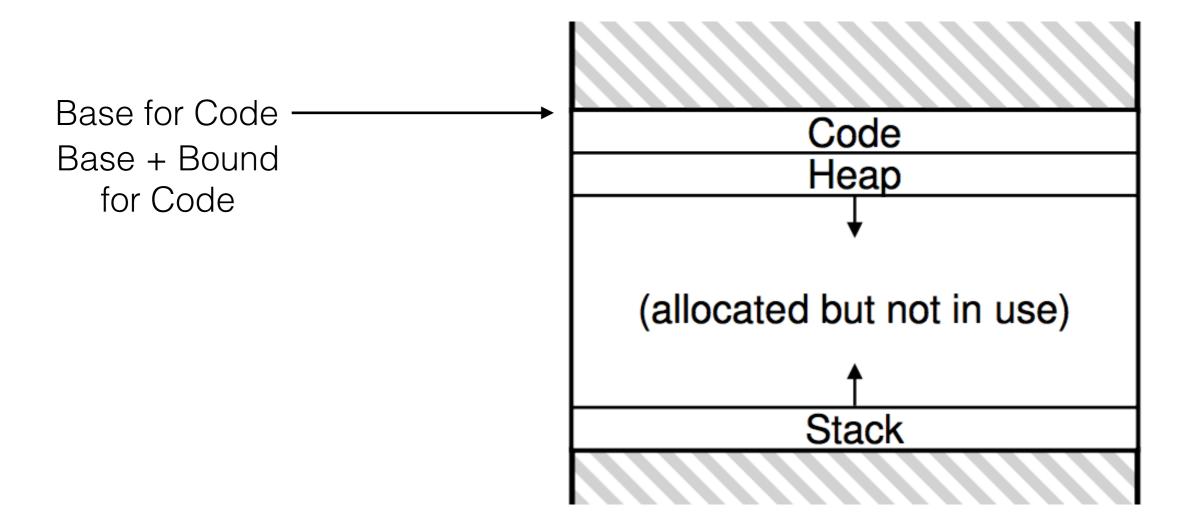

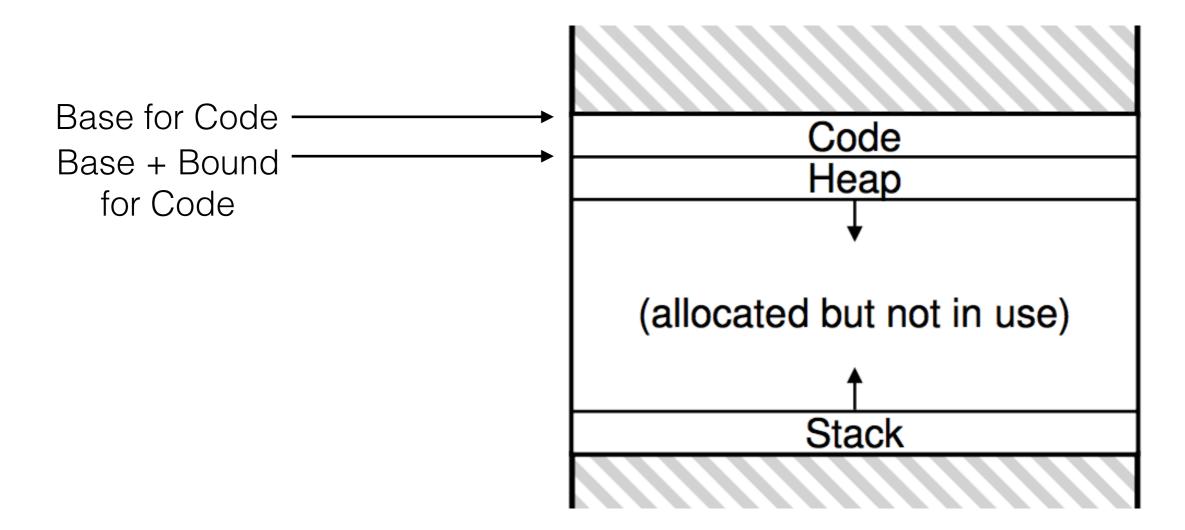

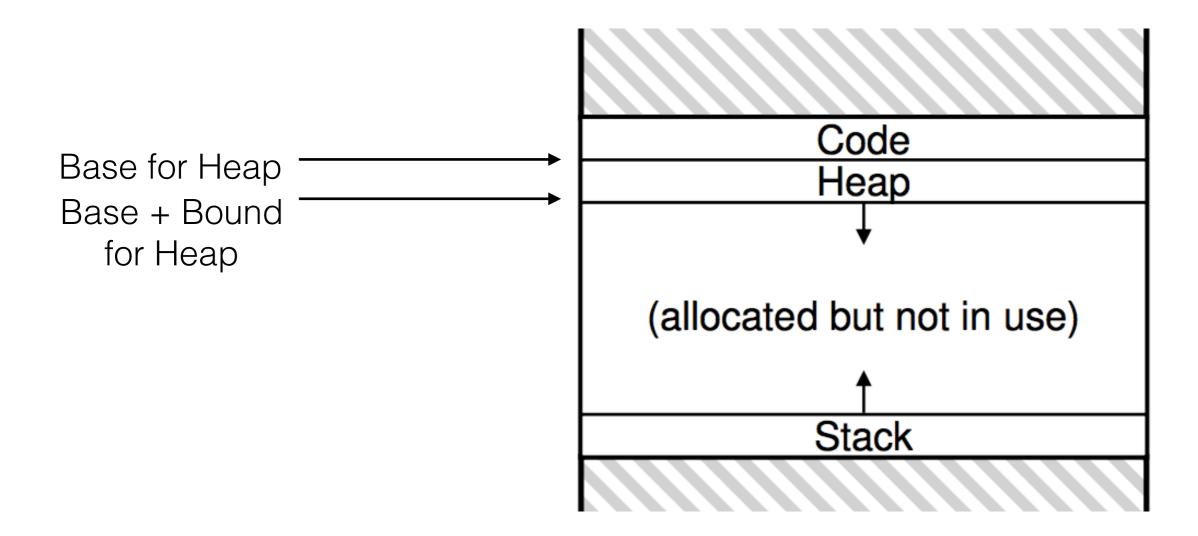

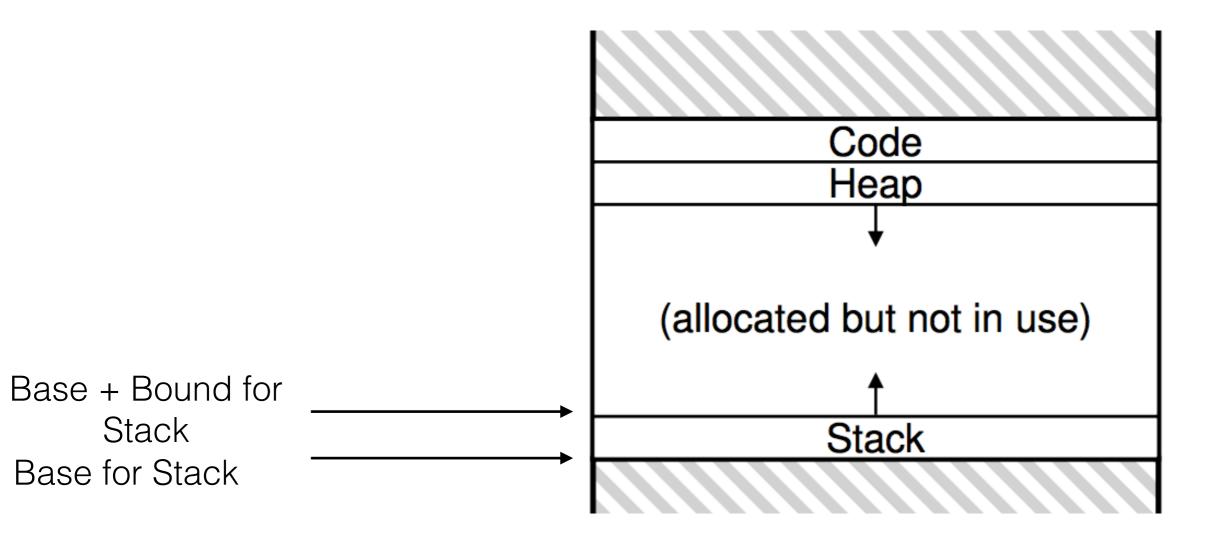

Base for Code Base + Bound for Code

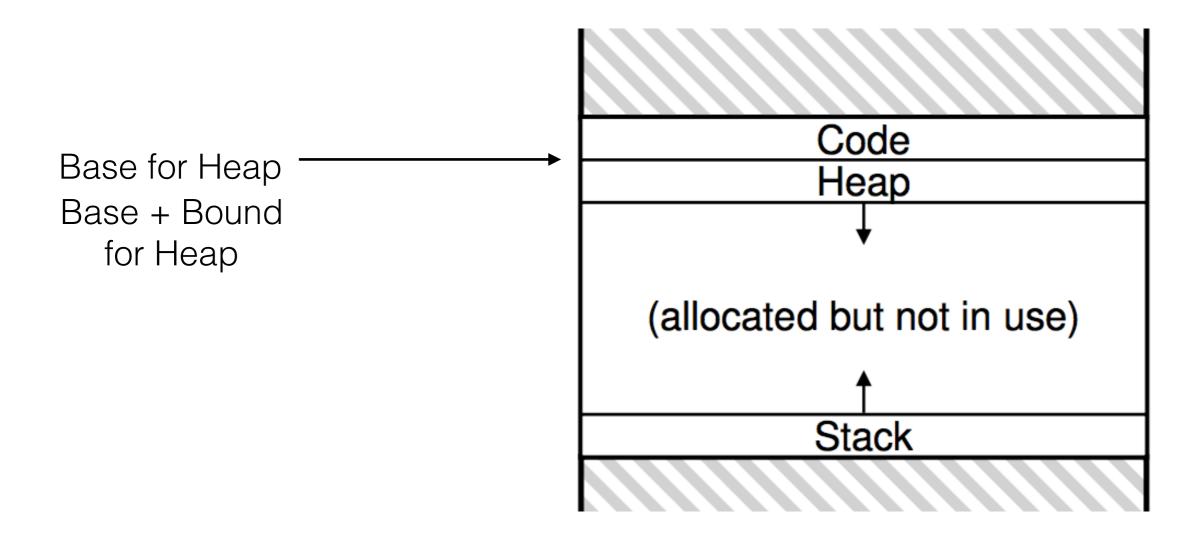

Base for Heap Base + Bound for Heap

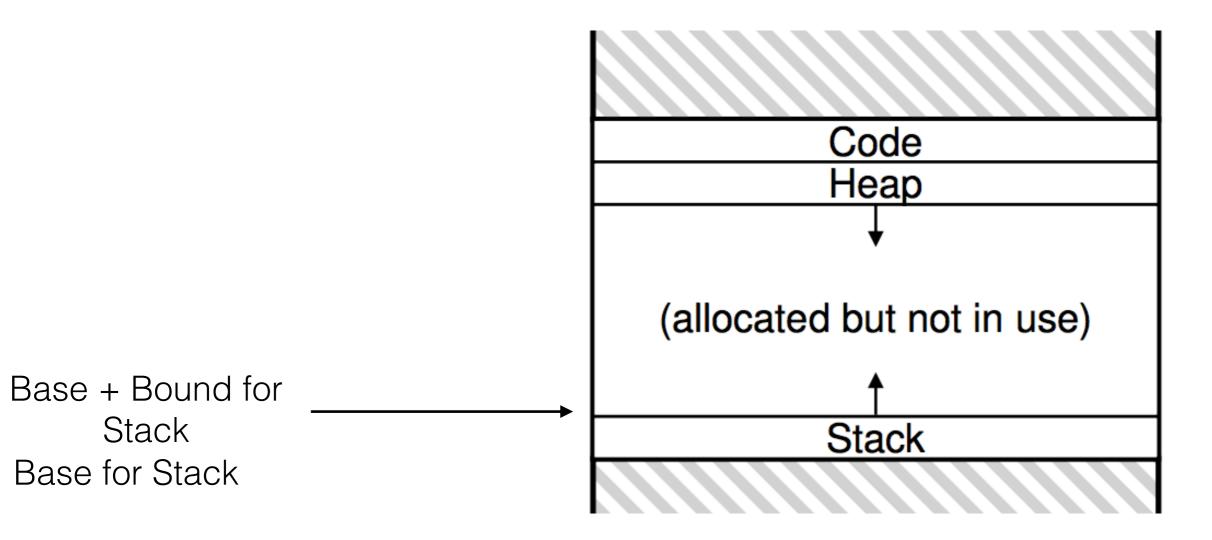

Base + Bound for Stack Base for Stack

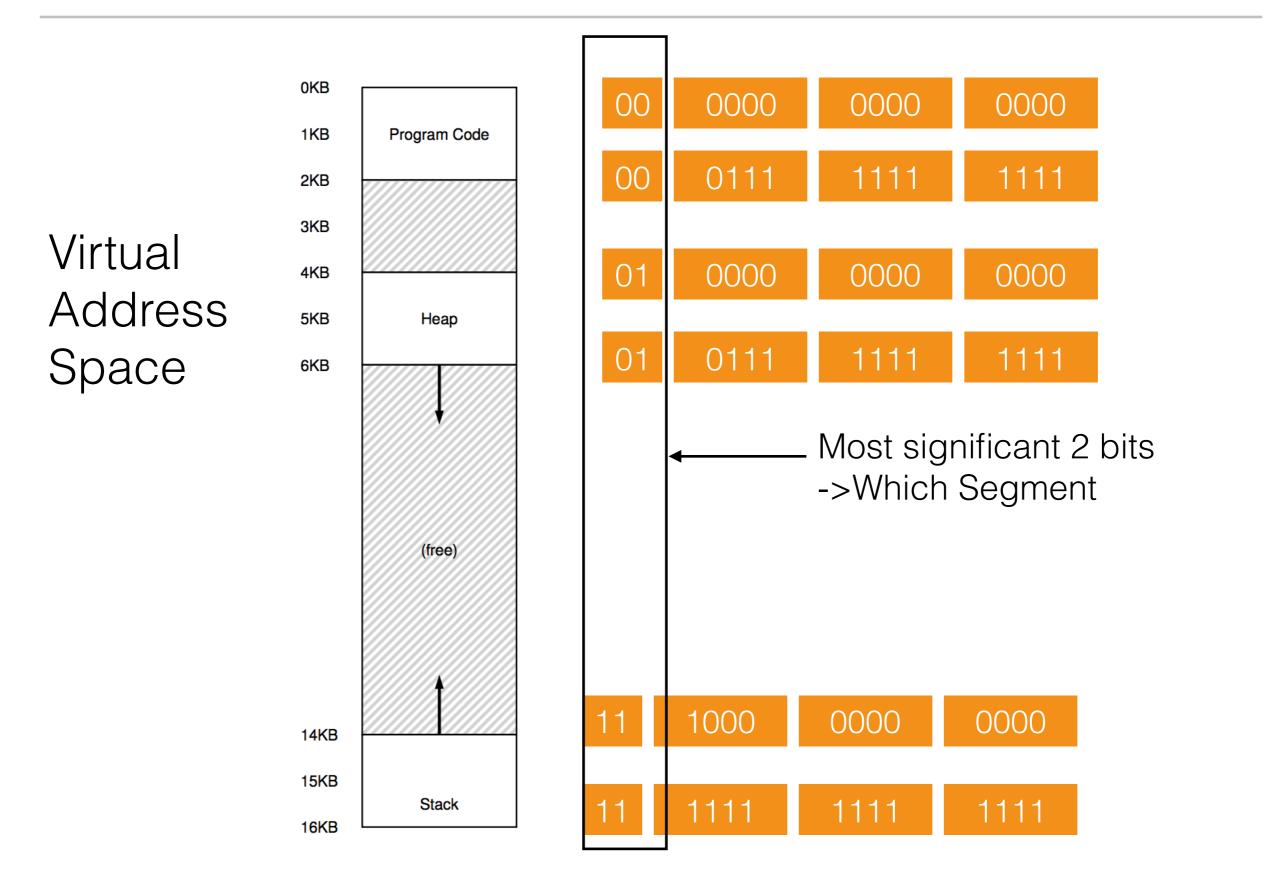

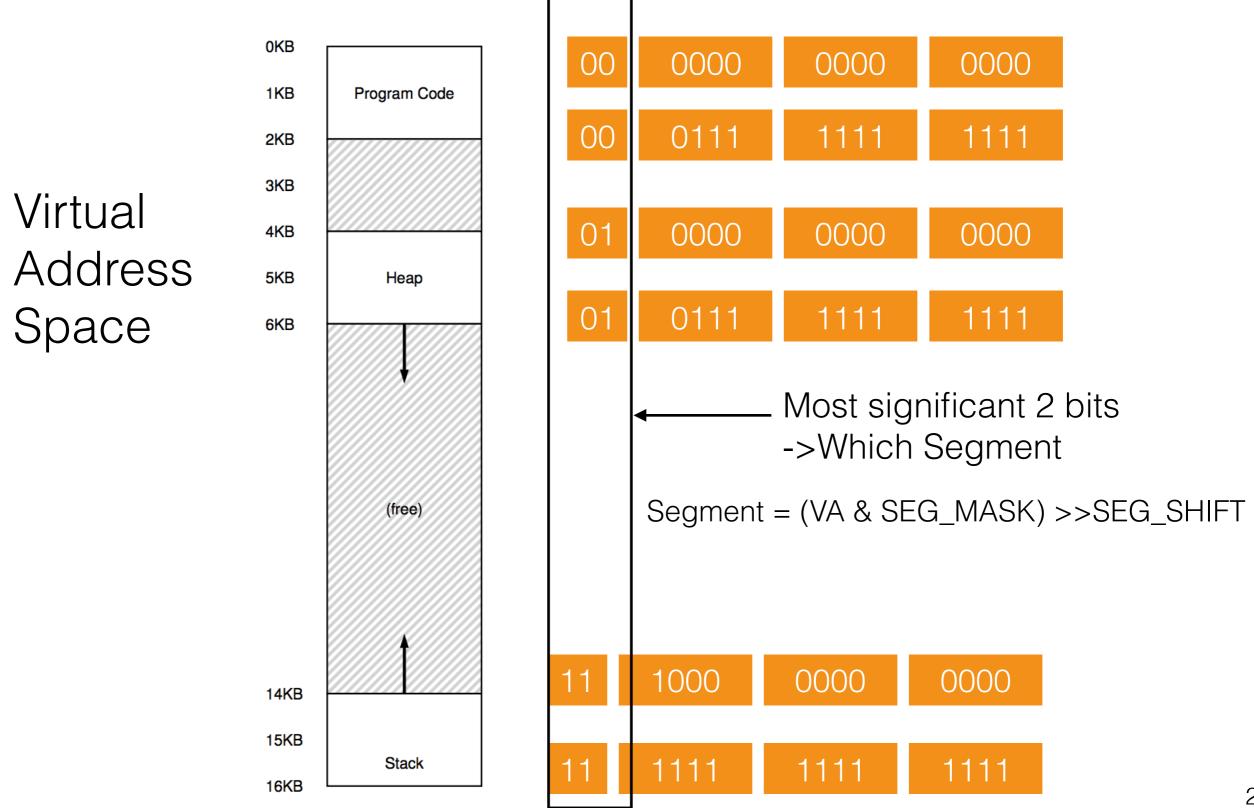

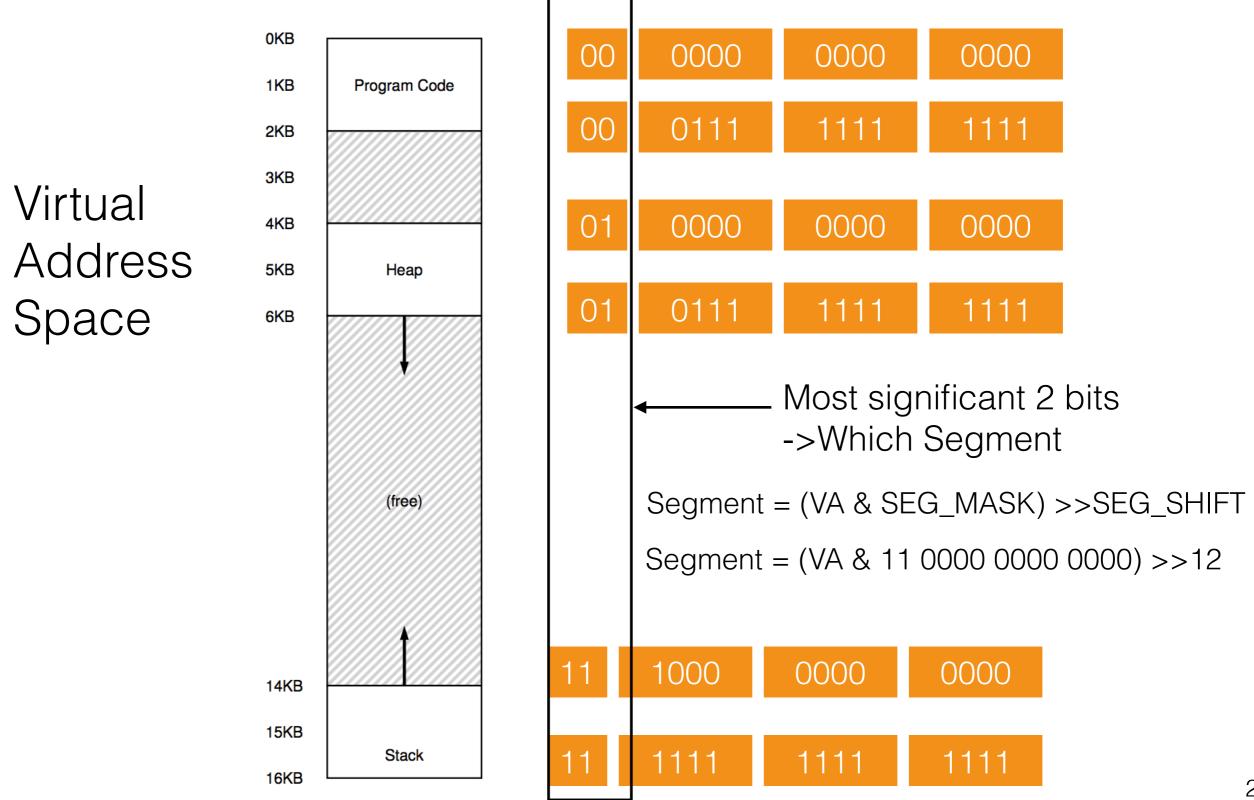

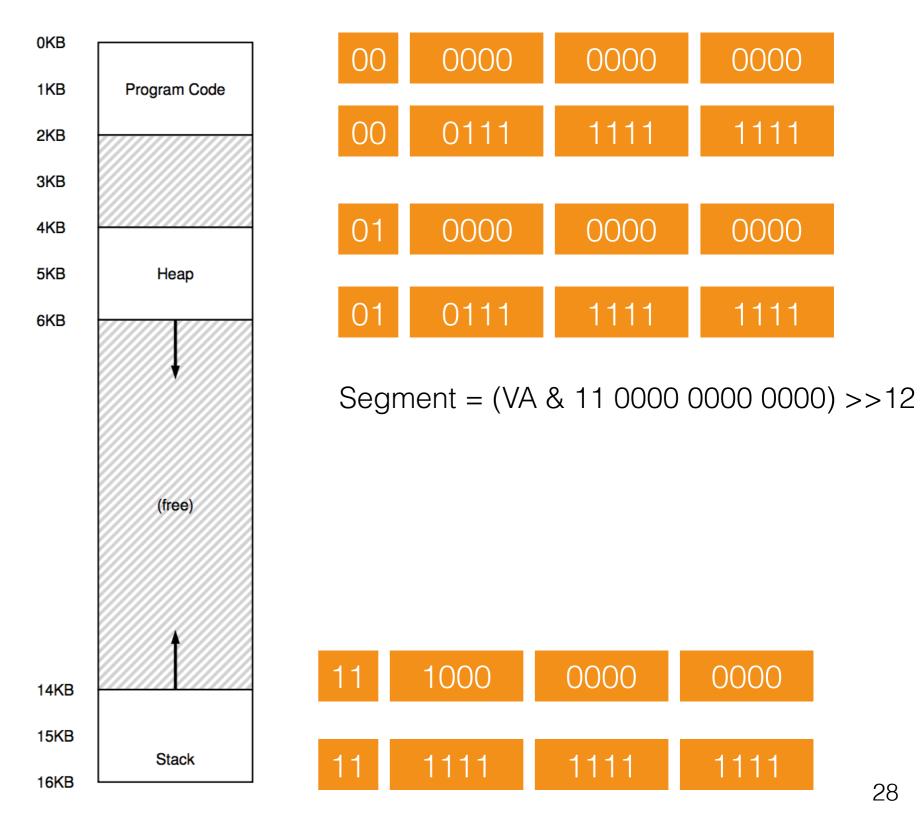

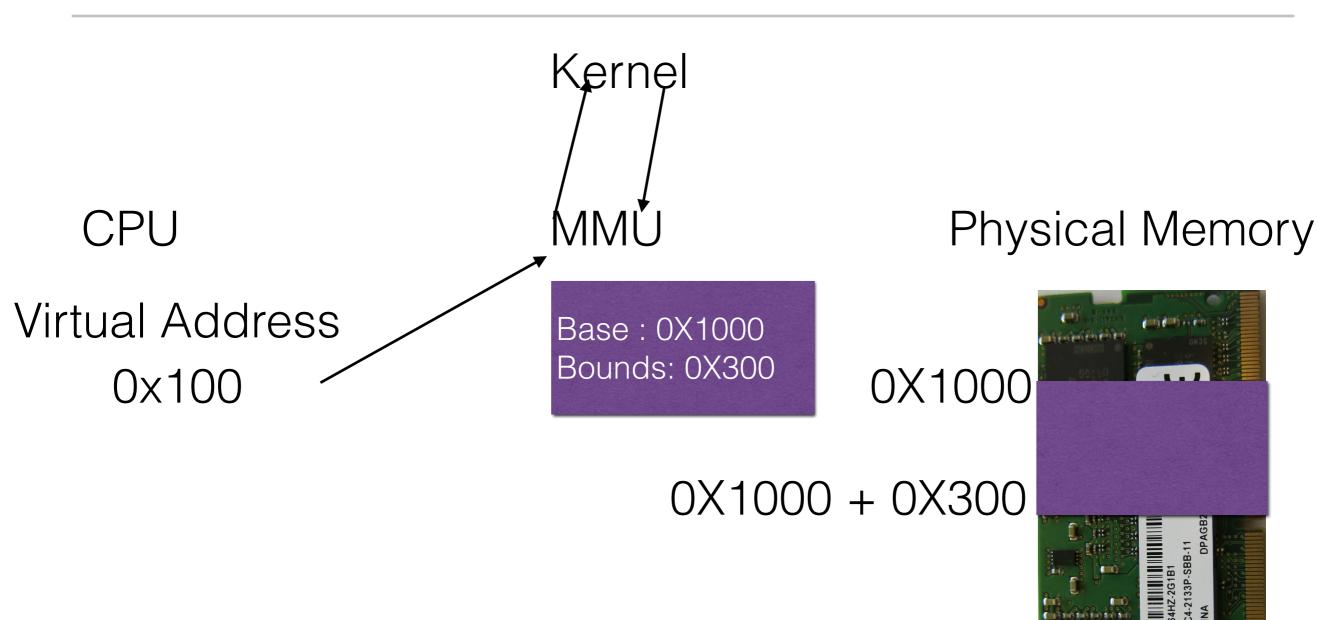

1. Multiple bases and bounds per process. Each of them called a segment.

- 1. Multiple bases and bounds per process. Each of them called a segment.

- 1. Each segment can have own size

- 1. Multiple bases and bounds per process. Each of them called a segment.

- 1. Each segment can have own size

- 2. Each segment can have own permissions:

- 1. Multiple bases and bounds per process. Each of them called a segment.

- 1. Each segment can have own size

- 2. Each segment can have own permissions:

- 1. Code would be?

### Segmentation

- 1. Multiple bases and bounds per process. Each of them called a segment.

- 1. Each segment can have own size

- 2. Each segment can have own permissions:

- 1. Code would be?

- 3. Each segment can have direction of growth!

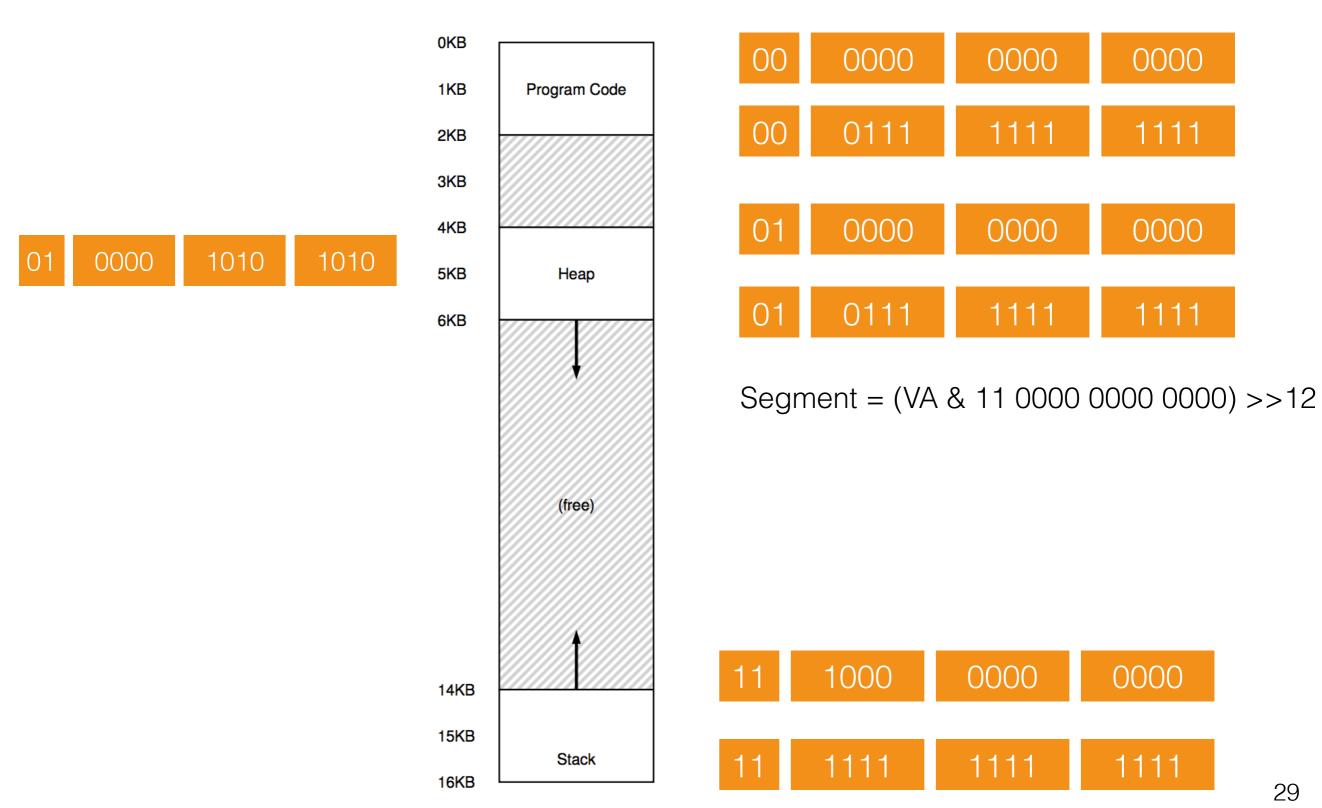

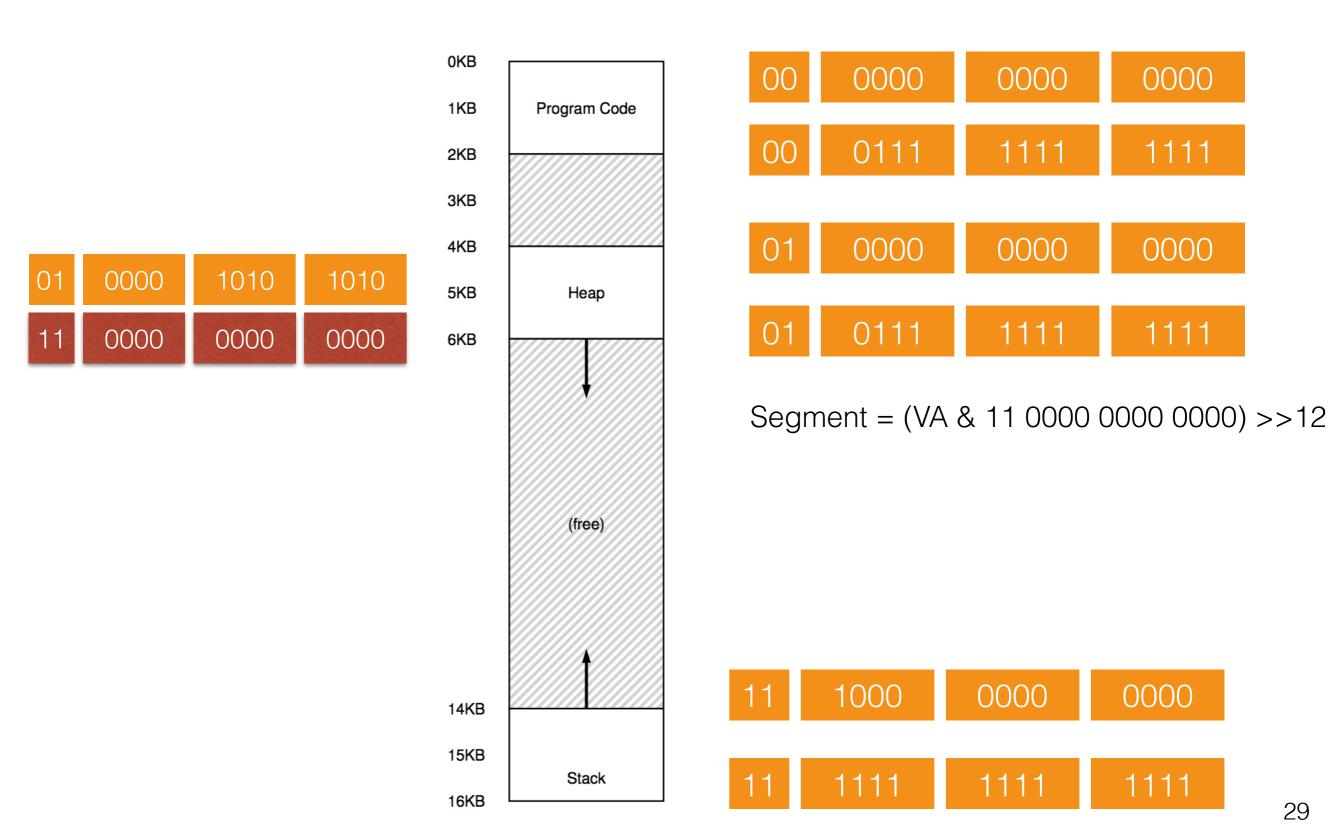

1. Each segment has:

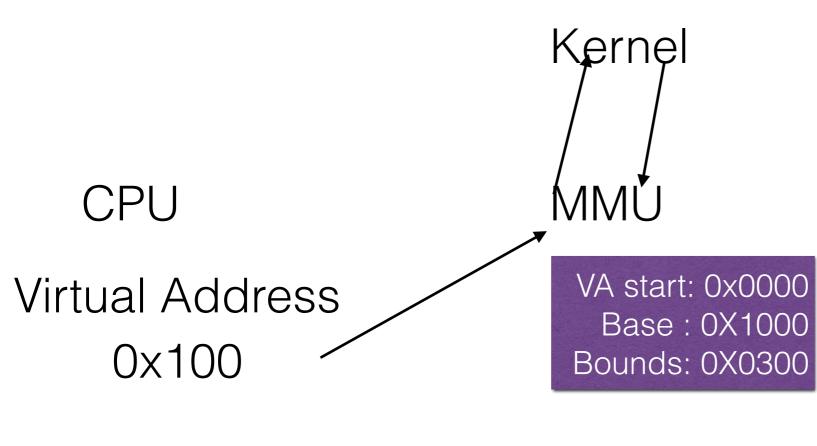

- 1. Each segment has:

- 1. Start virtual address (VA)

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 3. Bound

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 3. Bound

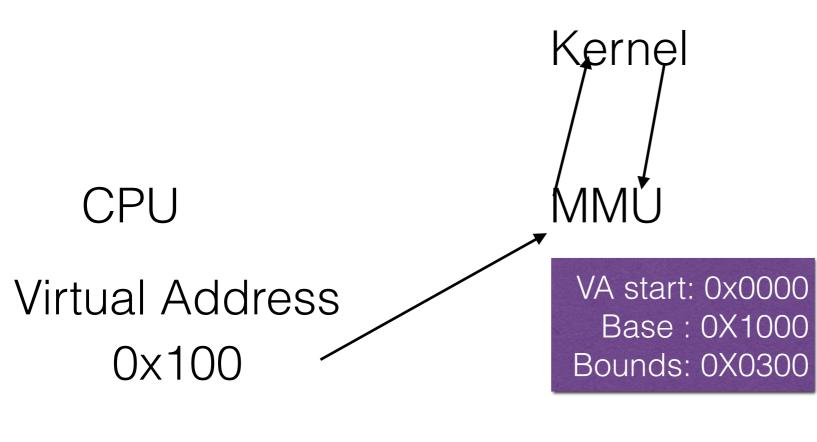

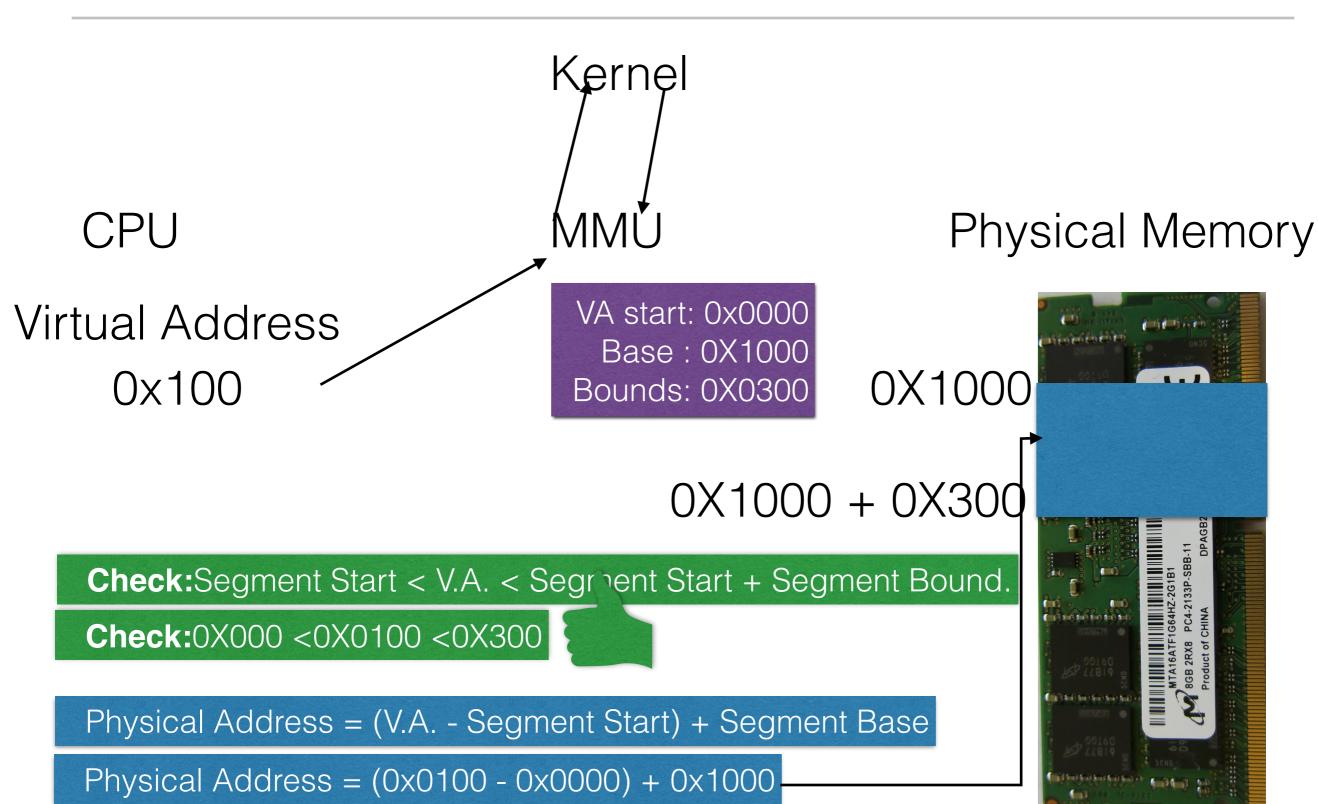

- 2. Check: Virtual Address is OK if it inside some segment, or for some segment:

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 3. Bound

- 2. Check: Virtual Address is OK if it inside some segment, or for some segment:

- 1. Segment Start < V.A. < Segment Start + Segment Bound.

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 3. Bound

- 2. Check: Virtual Address is OK if it inside some segment, or for some segment:

- 1. Segment Start < V.A. < Segment Start + Segment Bound.

- 3. **Translate**: For the segment that contains this virtual address:

- 1. Each segment has:

- 1. Start virtual address (VA)

- 2. Base physical address

- 3. Bound

- 2. Check: Virtual Address is OK if it inside some segment, or for some segment:

- 1. Segment Start < V.A. < Segment Start + Segment Bound.

- 3. **Translate**: For the segment that contains this virtual address:

- 1. Physical Address = (V.A. Segment Start) + Segment Base

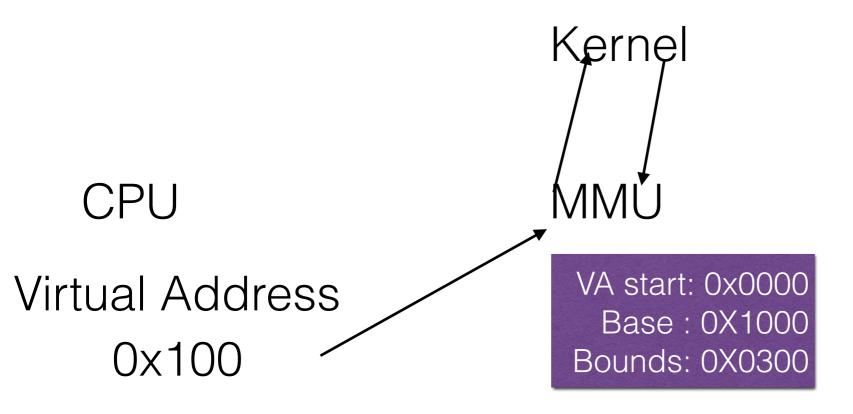

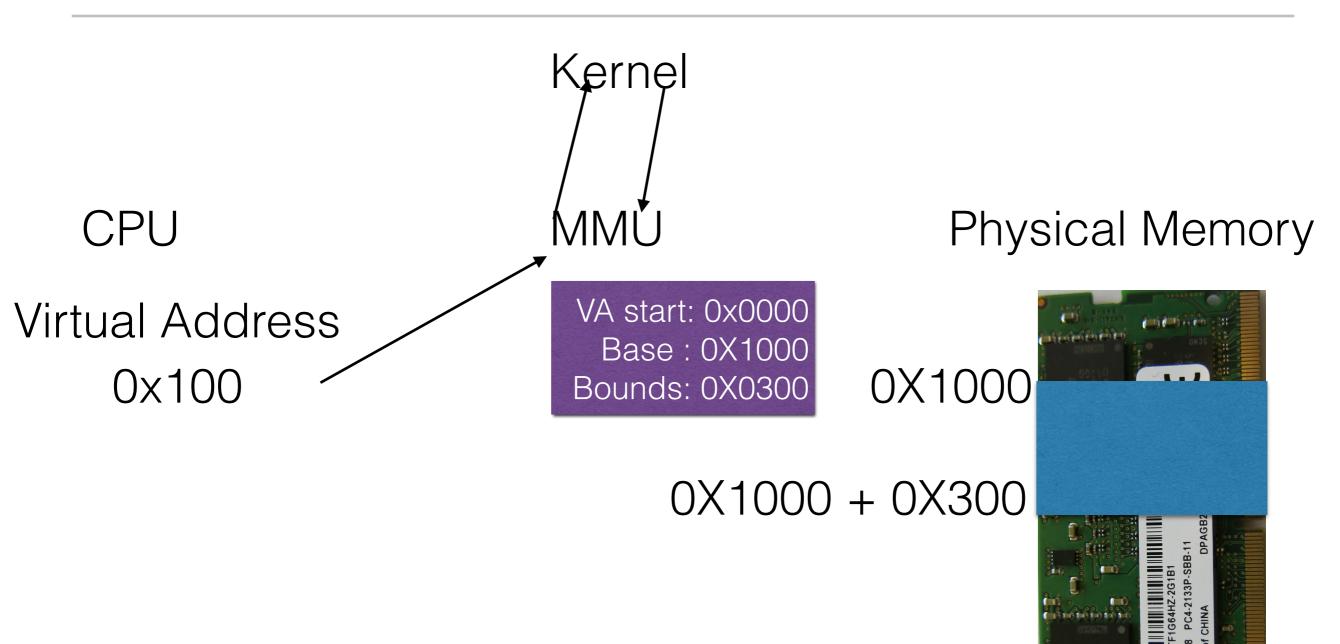

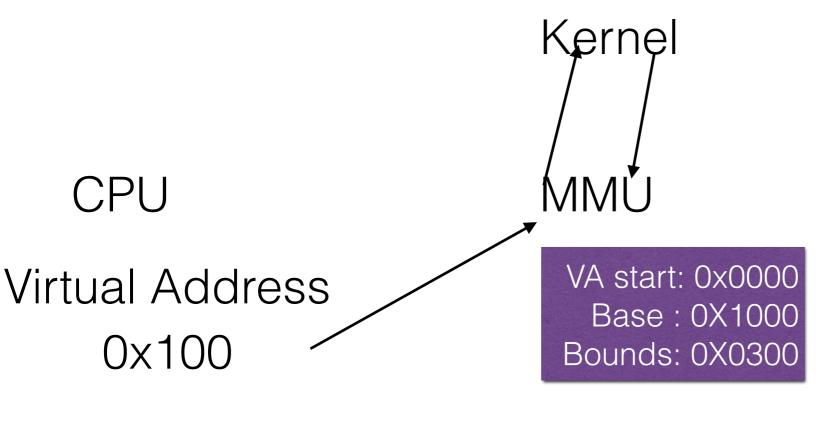

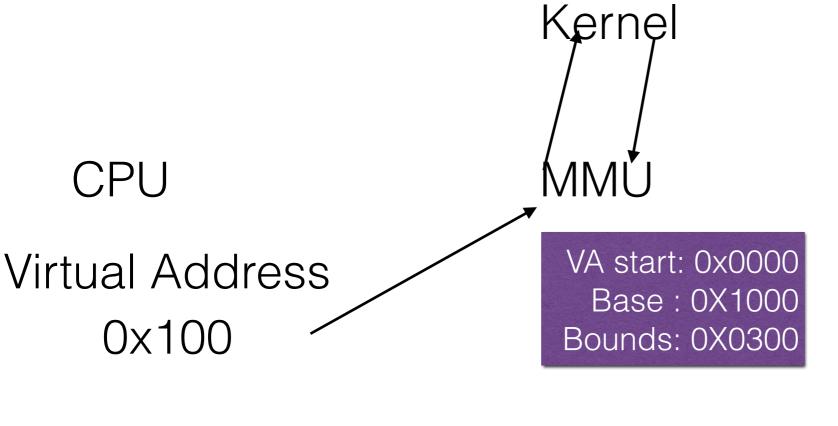

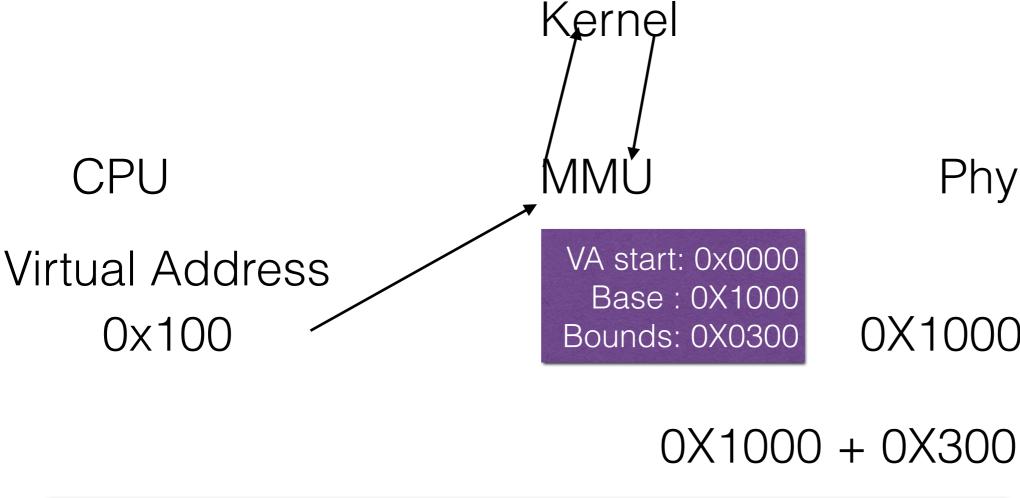

Kernel

CPU MMU

Virtual Address 0x100

Kernel

CPU MMU

Virtual Address

0x100

Physical Memory

0X1000

0X1000 + 0X300

Check: Segment Start < V.A. < Segment Start + Segment Bound.

Physical Memory

0X1000

0X1000 + 0X300

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X000 <0X0100 <0X300

Physical Memory

0X1000

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X000 <0X0100 <0X300

Physical Memory

0X1000

0X1000 + 0X300

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X000 <0X0100 <0X300

Physical Address = (V.A. - Segment Start) + Segment Base

Physical Memory

0X1000

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X000 <0X0100 <0X300

Physical Address = (0x0100 - 0x0000) + 0x1000

Kernel

CPU MMU

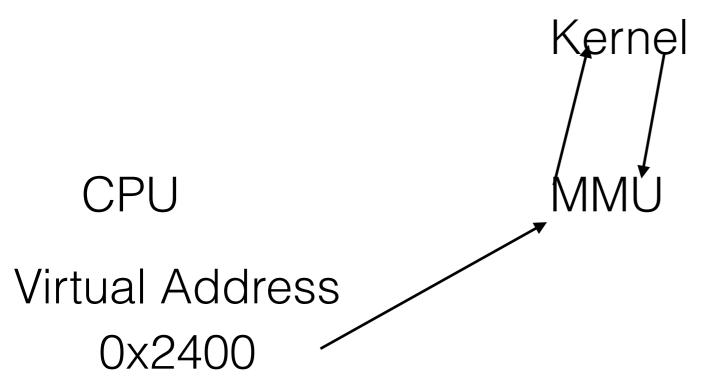

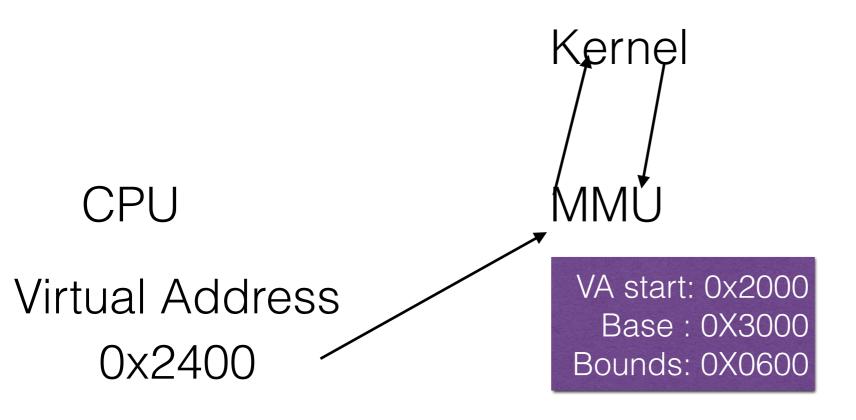

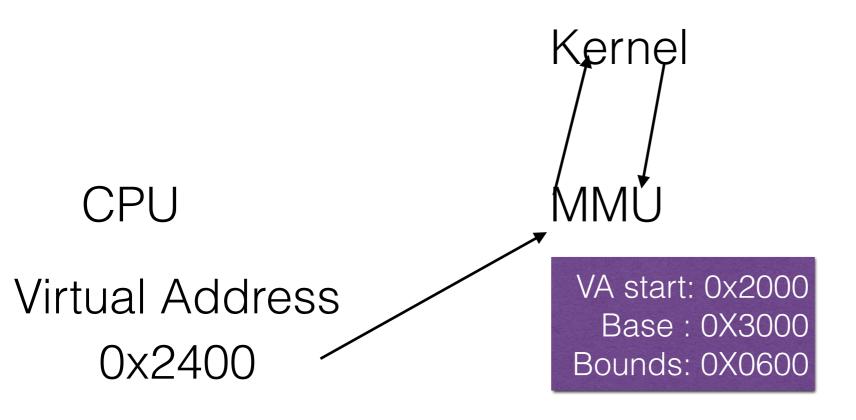

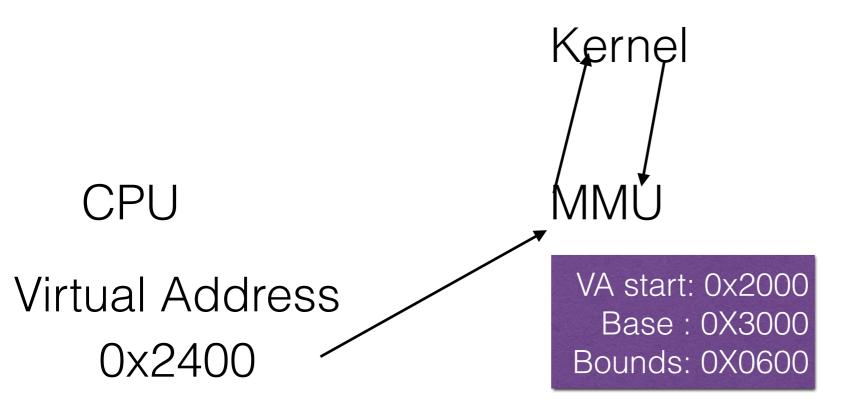

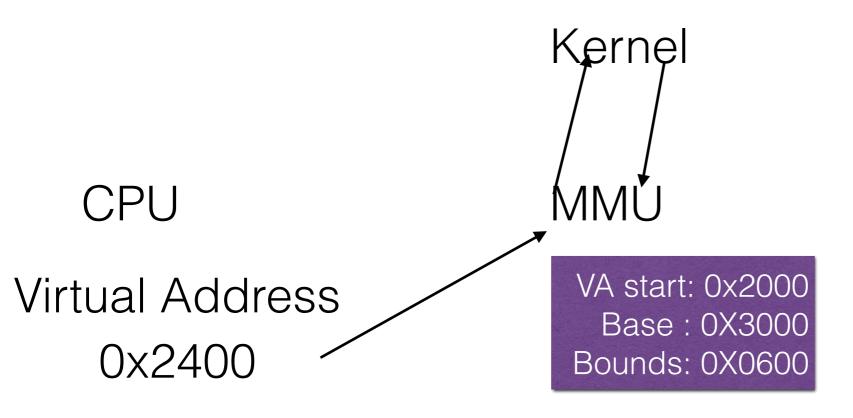

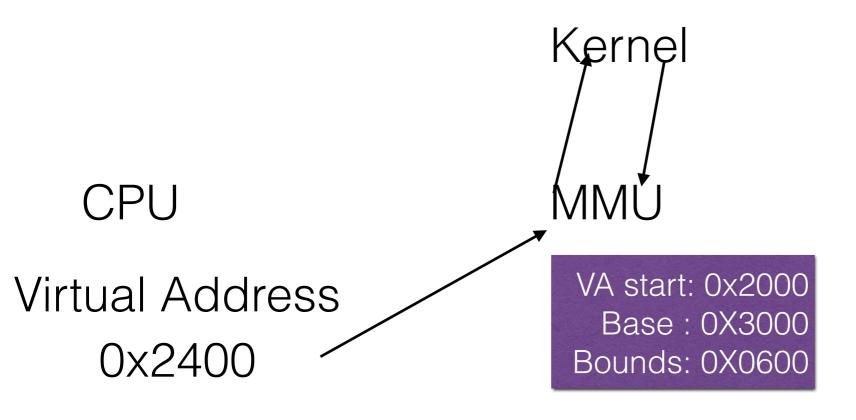

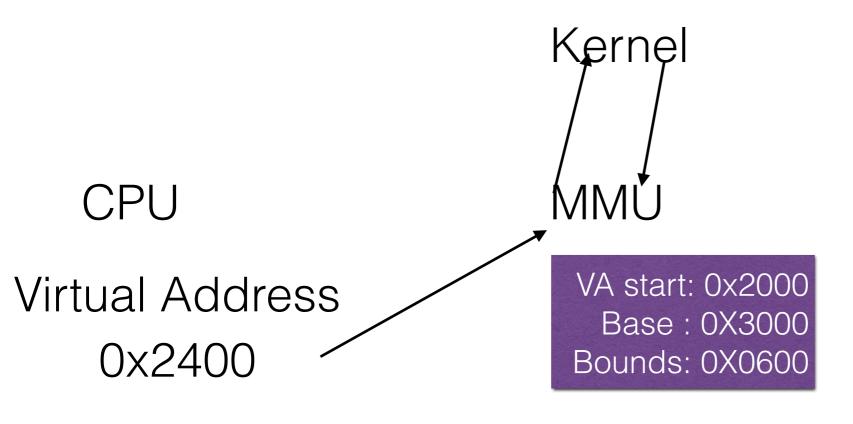

Virtual Address 0x2400

Kernel

CPU MMU

Virtual Address

0x2400

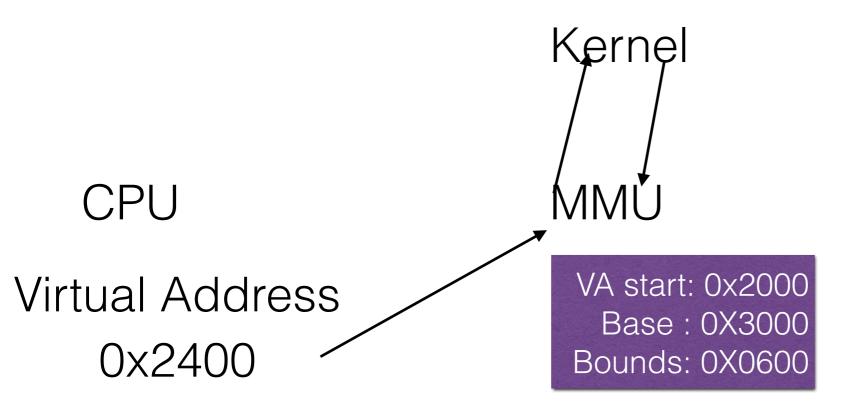

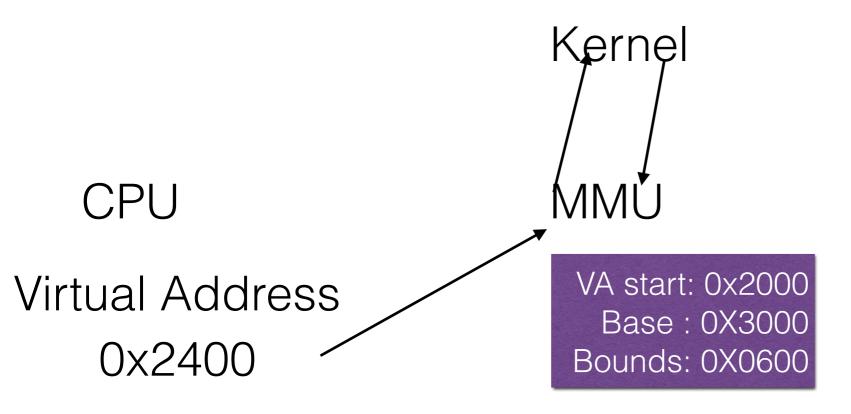

### Physical Memory

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X2000 <0X2400 <0X2000+0X600

Check: Segment Start < V.A. < Segment Start + Segment Bound.

#### Physical Memory

0X3000

**Check:**0X2000 <0X2400 <0X2000+0X600

Check: Segment Start < V.A. < Segment Start + Segment Bound.

### Physical Memory

#### Physical Memory

0X3000

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X2000 <0X2400 <0X2000+0X600

Physical Address = (V.A. - Segment Start) + Segment Base

#### Physical Memory

0X3000

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X2000 <0X2400 <0X2000+0X600

Physical Address = (V.A. - Segment Start) + Segment Base

Physical Address = (0x2400 - 0x2000) + 0x3000

### Physical Memory

0X3000

Check: Segment Start < V.A. < Segment Start + Segment Bound.

**Check:**0X2000 <0X2400 <0X2000+0X600

Physical Address = (0x2400 - 0x2000) + 0x3000

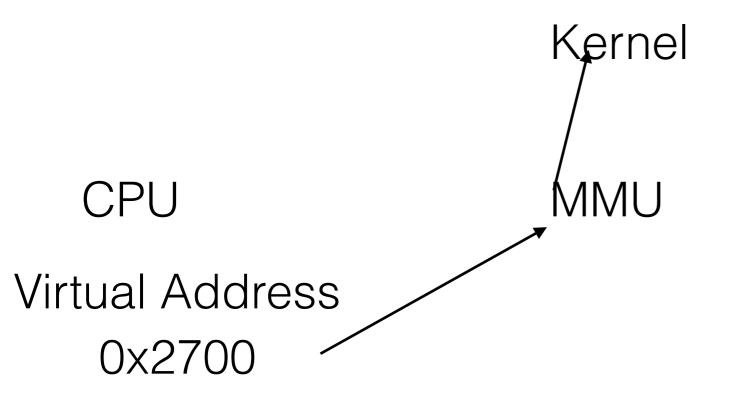

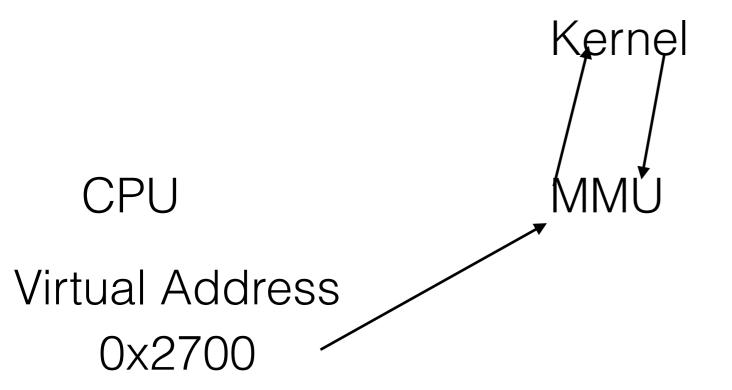

Kernel

CPU

MMU

Physical Memory

Virtual Address 0x2700

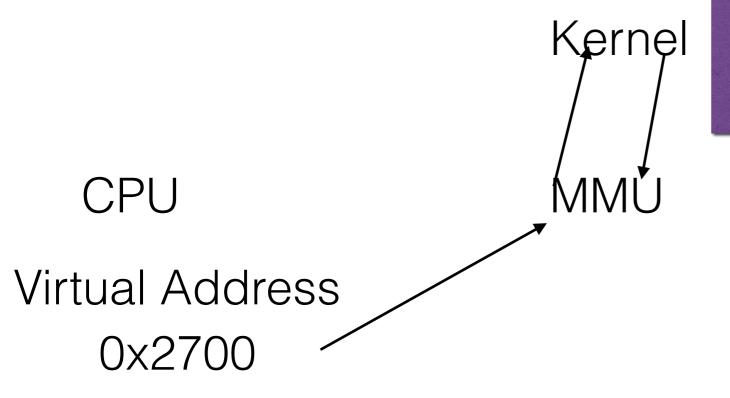

Kernel

CPU MMU

Virtual Address

0x2700

VA start: 0x0000 Base : 0X1000 Bounds: 0X0300

VA start: 0x0000 Base : 0X1000

Bounds: 0X0300

VA start: 0x2000 Base : 0X3000

Bounds: 0X0600

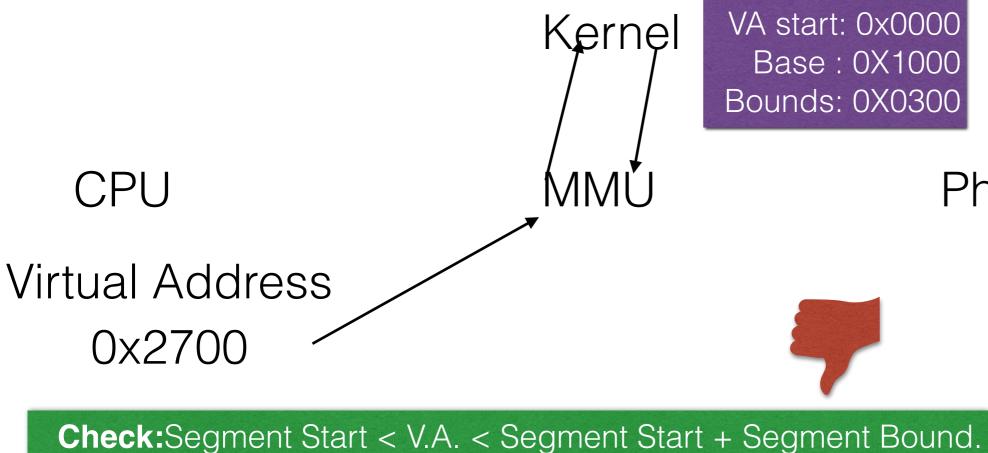

CPU MMU

Virtual Address

0x2700

**Check:**Segment Start < V.A. < Segment Start + Segment Bound.

VA start: 0x0000

Base: 0X1000

Bounds: 0X0300

VA start: 0x2000

Base: 0X3000

Bounds: 0X0600

Base : 0X1000 Base : 0X3000 bunds: 0X0300 Bounds: 0X0600

CPU MMU

Virtual Address

0x2700

VA start: 0x0000

Base: 0X1000

Bounds: 0X0300

VA start: 0x2000

Base: 0X3000

Bounds: 0X0600

Physical Memory

**Check:**Segment Start < V.A. < Segment Start + Segment Bound.

#### SEGMENTATION FAULT